Навигация

Устройства контроля четности (УКЧ)

9.1.2.4 Устройства контроля четности (УКЧ)

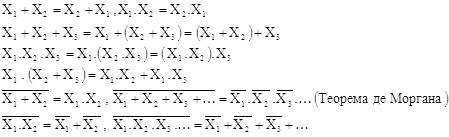

Предназначены для проверки двоичных кодовых комбинаций, поступающих на их входы, на наличие в них четного (нечетного) числа единиц. Такое КЦУ имеет n входов, равное количеству разрядов входного ДК, и один выход. На выходе формируется напряжение высокого уровня только в том случае, если число единиц во входном коде нечетное. Основу схемы контроля четности составляет сумматор по модулю два, реализующий логическую операцию

![]() .(9.14)

.(9.14)

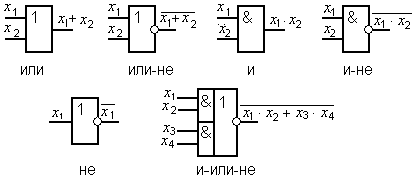

Для двух переменных эта операция может быть выполнена логическим элементом “ИСКЛЮЧАЮЩЕЕ ИЛИ”, который реализует логическую функцию

![]() .(9.15)

.(9.15)

Функция F имеет значение единица только в том случае, если в наборе из двух переменных имеется одна единица, в остальных случаях значение функции равно нулю.

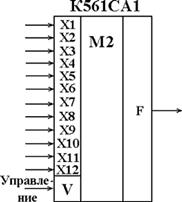

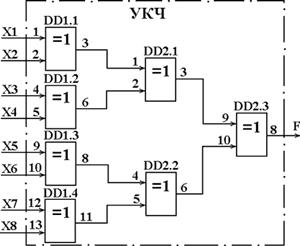

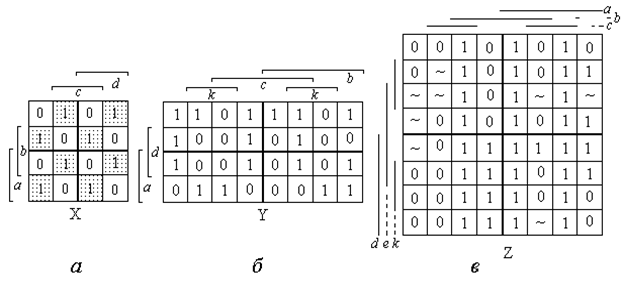

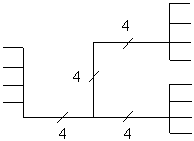

Ниже показаны: состав микросхемы К555ЛП5, включающей 4 двухвходовых сумматора по модулю два (рисунок 9.22, а), пример построения на основе ИМС К555ЛП5 устройства контроля четности 8-разрядного ДК (рисунок 9.22,б) и обозначение микросхемы К561СА1, являющейся устройством контроля четности 12-разрядных двоичных кодов (рисунок 9.22, в).

Если V = 0, то:

чет à F = 0; ü

ý F дополняет до четности.

нечет à F = 1;þ

Если V = 1, то:

чет à F = 1; ü

ý F дополняет до нечетности.

нечет à F = 0;þ

А Б

В

Рисунок 9.22

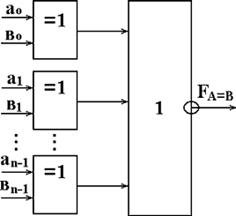

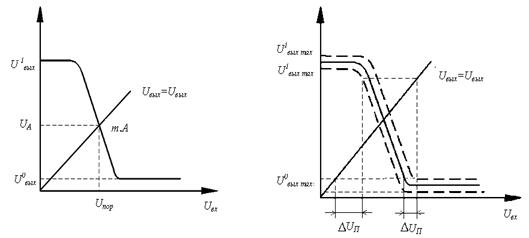

9.1.2.5 Цифровые компараторы

Сравнивают два числа, представленных в двоичном коде, А={an-1, an-2,..., a1, a0} и В= {вn-1, вn-2,..., в1, в0} и формируют признак результата сравнения в виде напряжения высокого уровня на одном из выходов: FA=B , FA<B , FA>B.

Рисунок 9.23

Наиболее простой является схема формирования признака равенства двух чисел (рисунок 9.23).

Такой компаратор включает логический элемент ИЛИ-НЕ, на входы которого подаются результаты поразрядного сложения по модулю два. Схема реализует логическую функцию

![]() .(9.16)

.(9.16)

После преобразования (9.13.1) по теореме де Моргана получим:

![]() . (9.17)

. (9.17)

Учитывая, что ![]() =

= ![]() – неэквивалентность (и сумма по модулю два для двух переменных), выражение (9.17) примет вид:

– неэквивалентность (и сумма по модулю два для двух переменных), выражение (9.17) примет вид:

![]() ,(9.18)

,(9.18)

что соответствует рисунку 9.23.

Если А=В, то F=1, если А¹В, то F=0.

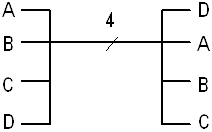

Ниже показаны: обозначение 4-входового компаратора на электрических схемах (рисунок 9.24, а) и пример его реализации на сумматоре и логических элементах И, ИЛИ-НЕ, НЕ (рисунок 9.24, б).

А

Б

Рисунок 9.24

9.1.3 Использование для проектирования КЦУ мультиплексоров, дешифраторов и постоянных запоминающих устройств

В связи с тем, что многие серии ИМС содержат в своем составе мультиплексоры, дешифраторы и постоянные запоминающие устройства (ПЗУ), то рассмотрим возможность реализации на их основе различных КЦУ. В ряде случаев, особенно при большом числе входных переменных и значительном количестве выходов это позволяет уменьшить общее число требуемых корпусов микросхем.

9.1.3.1 Построение КЦУ на мультиплексорах

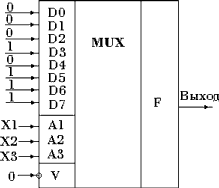

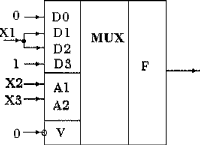

В качестве примера рассмотрим реализацию с помощью восьмивходового мультиплексора (рисунок 9.25) мажоритарного элемента, функционирование которого описано таблицей истинности (таблица 9.8).

На адресные входы мультиплексора подаются входные логические переменные Х1, Х2, Х3, а на информационных входах D0...D7 зафиксированы значения реализуемой логической функции на наборах логических переменных, номера которых совпадают с номерами информационных входов мультиплексора.

Рисунок 9.25

Таблица 9.8

| № набора | X3 | X2 | X1 | F | |

| 0 | 0 | 0 | 0 | 0 | Y0 |

| 1 | 0 | 0 | 1 | 0 | Y1 |

| 2 | 0 | 1 | 0 | 0 | Y2 |

| 3 | 0 | 1 | 1 | 1 | Y3 |

| 4 | 1 | 0 | 0 | 0 | Y4 |

| 5 | 1 | 0 | 1 | 1 | Y5 |

| 6 | 1 | 1 | 0 | 1 | Y6 |

| 7 | 1 | 1 | 1 | 1 | Y7 |

Имеется возможность вдвое сократить требуемое число информационных входов мультиплексора (а, следовательно, использовать более простую его структуру), если на эти входы подать не только фиксированные уровни логических единиц и нулей, но и значения отдельных входных переменных Х.

Таблица 9.9

| (A2) | (A1) | Информационные входы мультиплексора 4x1 (рисунок 9.26) | ||||

| № набора | X3 | X2 | X1 | F | D | |

| Гр.1 | 0 | 0 | 0 | 0 | 0 | D0=0 |

| 1 | 0 | 0 | 1 | 0 | ||

| Гр.2 | 2 | 0 | 1 | 0 | 0 | D1=X1 |

| 3 | 0 | 1 | 1 | 1 | ||

| Гр.3 | 4 | 1 | 0 | 0 | 0 | D2=X1 |

| 5 | 1 | 0 | 1 | 1 | ||

| Гр.4 | 6 | 1 | 1 | 0 | 1 | D3=1 |

| 7 | 1 | 1 | 1 | 1 |

Для этого еще раз изобразим таблицу истинности проектируемого мажоритарного элемента, разделив ее на четыре группы по две строки в каждой (таблица 9.9).

В пределах каждой группы возможны только четыре значения выходной булевой функции F: нулевое значение на обоих наборах – гр. 1; единичное значение на обоих наборах – гр.4: совпадение функции F с переменной Х1 (наборы 2, 3, 4, 5): противоположные значения функции F и переменной Х1 (в данном примере отсутствуют).

Следовательно, для реализации соответствующего КЦУ можно использовать четырехвходовой мультиплексор, на адресные входы которого подаются переменные Х3 и Х2, а на информационные входы D – значения в соответствии с последним столбцом таблицы 9.9 (рисунок 9.26).

Рисунок 9.26

В результате имеется возможность уменьшить аппаратные затраты используя для реализации трехвходового мажоритарного элемента лишь половину микросхемы К555КП2.

Похожие работы

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

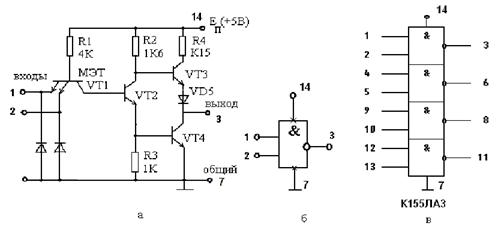

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

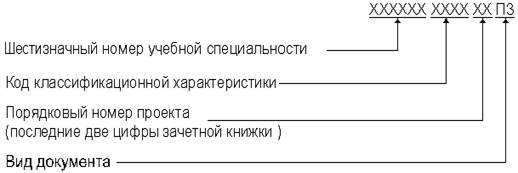

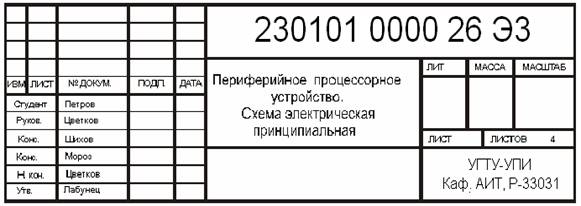

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев