Навигация

Триггеры в интегральном исполнении

9.2.1.2 Триггеры в интегральном исполнении

В современных сериях ИМС существует большое число различных триггеров.

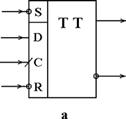

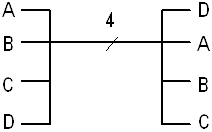

Ниже в качестве примера показаны обозначения двух широко используемых триггеров, выпускаемых в виде интегральной микросхемы (рисунок 9.42). Микросхема К555 ТМ2 включает два D-триггера с дополнительными S и R входами для установки схемы в исходное состояние (рисунок 9.42, а). Активными сигналами на S и R входах являются низкие уровни напряжений (логические нули).

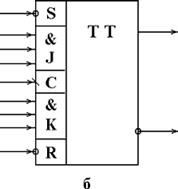

Микросхема К555 ТВ1 (рисунок 9.42, б) содержит один JK-триггер, включающий два асинхронных R и S входа для установки схемы в исходное состояние и два дополнительных трехвходовых конъюнктора, включенных на J и K входах. Дополнительные элементы И реализуют логические функции

J = J1. J2. J3, K= K1. K2. K3.(9.19)

Рисунок 9.42

Это расширяет возможности JK-триггера, например, упрощает построение синхронных счетчиков на подобных микросхемах.

9.2.2 Регистры

Регистрами называют последовательностные цифровые устройства, предназначенные для запоминания многоразрядных цифровых кодов и выполнения над ними некоторых логических преобразований. Основу регистров составляют триггеры, количество которых равно числу разрядов цифрового кода. Один триггер хранит 1 бит информации (один двоичный разряд), соответственно N-разрядный регистр способен хранить N бит информации. Кроме триггеров регистры содержат вспомогательные схемы, обеспечивающие прием кода в регистр, выдачу кода из регистра, сдвиг кода вправо или влево на требуемое число разрядов, преобразование параллельного кода в последовательный и наоборот, выполнение над отдельными разрядами регистра логических операций, например, И, ИЛИ, исключающее ИЛИ, установку регистра в начальное состояние (“СБРОС”) и др.

В зависимости от способа ввода и вывода разрядов числа регистры делятся на:

параллельные;

последовательные;

последовательно-параллельные;

параллельно-последовательные.

9.2.2.1 Параллельные регистры

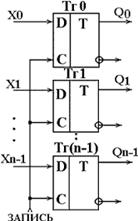

В таких регистрах ввод и вывод информации осуществляется в параллельной форме – одновременно всех разрядов.

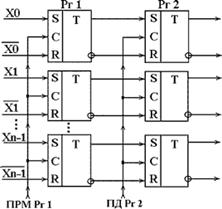

Рисунок 9.43

В зависимости от числа входных и выходных каналов параллельные регистры делятся на однофазные (каждый разряд передается по одному каналу в прямом коде) и парафазные (разряды передаются по двум каналам в прямом и обратном кодах).

На рисунке 9.43 показан пример двух параллельных регистров с парафазным вводом-выводом, выполненных на однотактных синхронных RSC-триггерах.

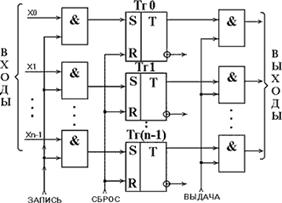

Рисунок 9.44

При парафазном обмене информацией на R, S входах любого триггера всегда присутствует комбинация сигналов Xi=1, ![]() , либо

, либо ![]() , устанавливающая его в требуемое состояние независимо от того, в каком состоянии этот триггер находился до этого, т.е. установка регистра в исходное состояние не требуется.

, устанавливающая его в требуемое состояние независимо от того, в каком состоянии этот триггер находился до этого, т.е. установка регистра в исходное состояние не требуется.

Под действием сигнала ПРМ Рг1 (прием в регистр 1) n-разрядный код записывается в регистр Рг1, а сигналом ПД Рг2 (передача в регистр 2) – передается в Рг2.

На рисунке 9.44 показан параллельный регистр, с однофазным обменом информации, выполненный на асинхронных RS-триггерах и конъюнкторах.

Так как информационные сигналы, поступающие только на S входы, не могут установить соответствующие триггеры в состояние 0 (из-за чего число может быть записано с ошибкой), то перед записью все триггеры регистра обнуляются сигналом “СБРОС”.

Следует отметить, что данная особенность характерна только для регистров с однофазной записью, выполненных на RS-триггерах. Если в качестве элемента памяти использовать D-триггеры, то их предварительное обнуление при однофазной записи не требуется (рисунок 9.45).

Рисунок 9.45

9.2.2.2 Последовательные (сдвигающие) регистры

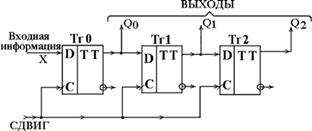

В таких регистрах триггеры соединены последовательно, и число вводится и выводится последовательно разряд за разрядом (рисунок 9.46).

Рисунок 9.46

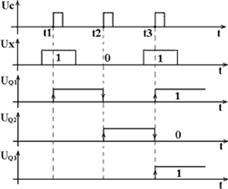

Рассматриваемый в примере последовательный регистр выполнен на D-триггерах. Записываемое в него число поступает по одному общему информационному входу Х в последовательном коде (значения разрядов передаются последовательно друг за другом). При поступлении первого импульса сдвига на синхровходы в каждом триггере записывается значение логического сигнала на его входе: Q0t+1 = X; Q1t+1 = Q0t; Q2t+1 = Q1t.

Эта информация хранится до поступления второго импульса сдвига, после чего записанный перед этим код сдвинется вправо на один разряд, а в триггер Тг0 запишется новое значение входного информационного сигнала. Третий импульс сдвига вновь сдвинет содержимое регистра вправо на один разряд и запишет в Тг0 информационный бит.

Сказанное иллюстрируют временные диаграммы работы, на которых предполагается, что все триггеры регистра находятся в нулевом исходном состоянии (рисунок 9.47).

Рисунок 9.47

Анализируя работу последовательного регистра можно отметить следующее:

1) поступившее на вход Х регистра число 101 после третьего импульса на входе С оказывается записанным в разрядах триггера: Q3 =1, Q2 =0, Q1 =1. В общем случае, n - разрядный регистр заполняется n - разрядным числом за n тактовых импульсов;

2) поступивший на вход Х последовательный код преобразуется в регистре в параллельный код, и записанное число может быть считано с выходов триггеров Q3, Q2, Q1 параллельно (одновременно);

3) с поступлением каждого тактового импульса на вход С записанная в регистр информация сдвигается (движение происходит от входа к выходу), поэтому последовательный регистр называется сдвигающим регистром (регистром сдвига);

4) информация, записанная в последовательный регистр, может быть считана с его выхода (на рисунке 9.46 – Q2) в последовательном коде. Для этого после записи данных в регистр необходимо вновь подавать тактовые импульсы на вход С. Число поразрядно будет появляться на выходе (Q2 на рисунке 9.46) и оттуда может приниматься считывающим устройством.

Последовательный регистр осуществляет не только запись и хранение информации, но и преобразование формы ее представления.

Похожие работы

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

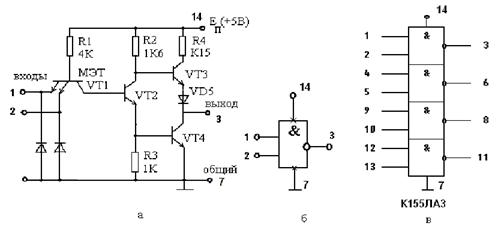

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

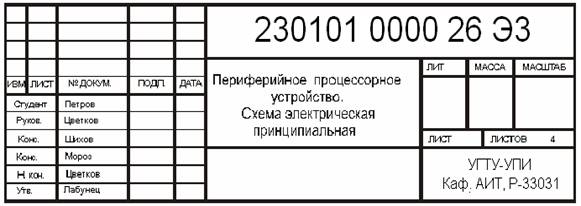

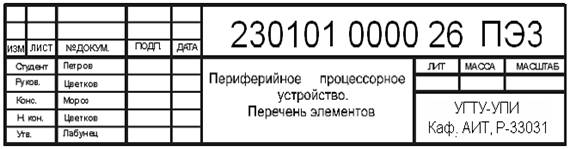

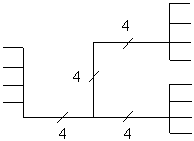

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев