Навигация

Шифраторы двоично-десятичного кода

9.1.2.1.2 Шифраторы двоично-десятичного кода

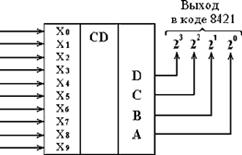

Шифраторы двоично-десятичного кода преобразуют входной десятичный (унитарный) код в двоично-десятичный (BCD)-код (код 8421). С выхода такого шифратора параллельно снимается группа двоичных сигналов, из которых каждые четыре (тетрада) отображают в двоичном коде десятичную цифру. Отличие четырехразрядного двоичного кода от четырехразрядного BCD-кода заключается в диапазоне изменения комбинаций выходного кода: в первом случае выходной код изменяется от 0000 до 1111, а во втором – от 0000 до 1001.

В одном байте (восьми битах) можно упаковать (уложить) две десятичные цифры в BCD-коде. Такой формат представления десятичных чисел называется упакованным.

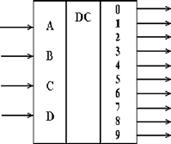

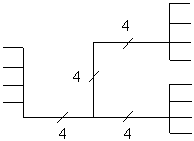

На рисунке 9.6 приведено функциональное обозначение шифратора BCD-кода.

На вход системы поступают двоичные цифры от 0 до 9, которые отображаются на выходе одной тетрадой двоичного кода, принимающей значения от 0000 В до 1001 В.

Рисунок 9.6

9.1.2.1.3 Дешифраторы двоичного кода

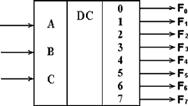

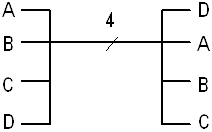

Дешифратором (декодером) двоичного кода называют КЦУ, преобразующее входной двоичный код в десятичный (унитарный). Полный дешифратор с m входами имеет 2m выходов. Каждой комбинации входных сигналов соответствует активное значение только одного определенного выходного сигнала. Ниже показана таблица истинности (таблица 9.4) и условное обозначение (рисунок 9.7) трехвходового полного дешифратора с единичными активными значениями выходных сигналов F0...F7.

Рисунок 9.7

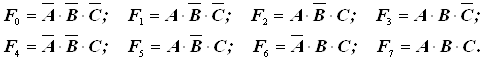

Дешифратор реализует восемь различных логических функций:

Таблица 9.4

| № набора | C | B | A | F0 | F1 | F2 | F3 | F4 | F5 | F6 | F7 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 3 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 6 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Если входные переменные рассматривать как двоичную запись чисел, то логическая единица формируется на том выходе, номер которого соответствует десятичному эквиваленту входного двоичного числа.

Рассмотренный дешифратор (таблица 9.4) является преобразователем двоичного кода в унитарный (десятичный).

Приведенные булевы выражения функций F0...F7 можно реализовать на логических элементах в базисах И, ИЛИ, НЕ; И-НЕ или ИЛИ-НЕ, пользуясь методикой изложенной ранее.

В интегральном исполнении выпускаются различные структуры дешифраторов, в которых имеются 2, 3 или 4 входа. В одном корпусе может быть несколько дешифраторов.

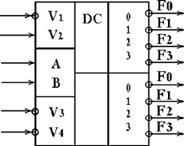

Для увеличения функциональных возможностей устройств часто предусматривается использование нескольких дополнительных сигналов управления. В качестве примера на рисунке 9.8 дано изображение микросхемы К555ИД4, содержащей сдвоенный двухвходовый дешифратор с активными нулевыми выходными сигналами.

Рисунок 9.8

Выходные сигналы обоих дешифраторов зависят от комбинации входных сигналов А, В. Синхронизация процесса формирования выходных сигналов F0...F3 для каждого дешифратора задается комбинациями управляющих сигналов V. Работу верхнего дешифратора разрешает комбинация V1=0, V2=1, а работу нижнего- V3=0, V4=0. Введение такого управления расширяет возможности микросхемы при построении более сложных устройств, например, дешифраторов с увеличенным числом входов и выходов.

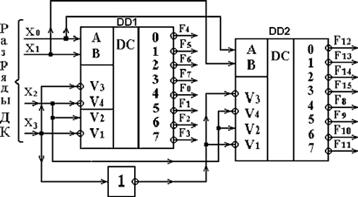

На рисунке 9.9 показан пример включения двух микросхем К555ИД4 для реализации дешифратора четырехразрядного входного двоичного кода в выходной шестнадцатипозиционный унитарный (десятичный) код. Работу этого дешифратора поясняют таблицы 9.4.1 и 9.4.2.

Рисунок 9.9

Таблица 9.4.1

| X3 | X2 | Рабочий дешифратор |

| 0 | 0 | Нижний ИМС DD1 |

| 0 | 1 | Верхний ИМС DD1 |

| 1 | 0 | Нижний ИМС DD2 |

| 1 | 1 | Верхний ИМС DD2 |

Таблица 9.4.2

| № набора | X3 | X2 | X1 | X0 | F0 | F1 | F2 | F3 | F4 | F5 | F6 | F7 | F8 | F9 | F10 | F11 | F12 | F13 | F14 | F15 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 5 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 10 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 11 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 13 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

Дешифраторы могут быть неполными (имеющими число выходов Nвых<2m, где m – число входных переменных). Например, такие дешифраторы могут использоваться для преобразования двоично-десятичного кода в код, предназначенный для управления десятичным индикатором (дешифраторы 4х10). На рисунке 9.10 показано условное обозначение дешифратора 4х10 (например, микросхемы К555ИД1 или К564ИД1). Схема имеет активные единичные выходные сигналы.

Рисунок 9.10

Похожие работы

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

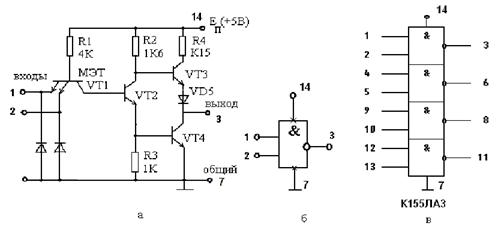

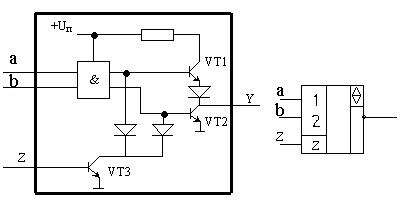

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

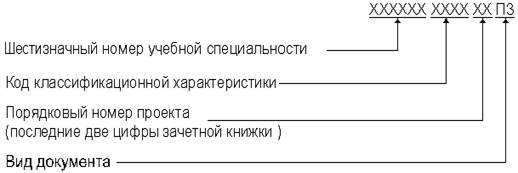

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев