Навигация

Базовый ЭСЛ - элемент ИЛИ/ИЛИ-НЕ

7.2 Базовый ЭСЛ - элемент ИЛИ/ИЛИ-НЕ

В этом элементе [3, 11] логические операции выполняются эмиттерно-связанными транзисторами, чем и обусловлено название типа логики. Элемент имеет два выхода, на одном из которых фиксируется результат операции ИЛИ над входными цифровыми сигналами, а на другом - операции ИЛИ-НЕ.

В этой схеме к “земле” присоединена плюсовая шина источника питания, поэтому выходные сигналы имеют отрицательную полярность.

Разработанные на основе схем ЭСЛ ИМС характеризуются высоким быстродействием, высокой нагрузочной способностью, низкой помехоустойчивостью и достаточно большой потребляемой мощностью.

7.3 Базовый КМОП-элемент ИЛИ-НЕ

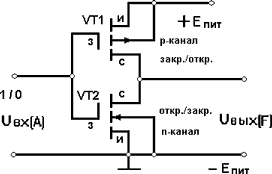

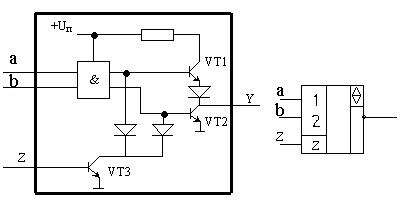

Логические схемы на комплементарных (дополняющих друг друга) МОП (МДП) - транзисторах содержат последовательно включенные и управляемые одним сигналом МОП-транзисторы с каналами разных типов проводимости (n- и p-типа) (рисунок 7.6).

Рисунок 7.6

Когда один из последовательно включенных транзисторов открывается, другой - закрывается. Поэтому такой каскад практически не потребляет мощности в статическом режиме.

КМОП-элемент (рисунок 7.6) представляет собой делитель напряжения +Епит. Нижнее плечо делителя составляет транзистор VT2, который называется коммутирующим или управляющим. Верхнее плечо образует транзистор VT1, который называется нагрузочным. Если на вход подается высокий уровень напряжения (логическая 1), то открывается транзистор VT2 и закрывается VT1. Большая часть напряжения питания выделяется на нагрузочном транзисторе VT1, а с выхода снимается низкий уровень напряжения (логический 0).

Если на вход поступает низкий уровень сигнала (логический 0), то открывается VT1 и закрывается VT2. С выхода снимается высокий уровень напряжения, а открытый транзистор VT1 выполняет функцию стокового резистора Rс. Рассмотренная схема выполняет функцию инвертора ![]() .

.

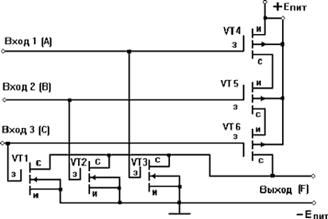

Ниже показана схема логического элемента с тремя входами ИЛИ-НЕ на КМОП-транзисторах (рисунок 7.7).

Рисунок 7.7

Если на любой из входов, например, С, подается высокий уровень (логическая 1), то открывается транзистор VT1 и шунтирует параллельно включенные с ним транзисторы VT2 и VT3. Сопротивление нижнего плеча делителя, состоящего из трех параллельно включенных управляющих транзисторов VT1, VT2 и VT3, уменьшается. Одновременно запирается транзистор VT6 и сопротивление верхнего плеча делителя, состоящего из трех последовательно включенных нагрузочных транзисторов VT4, VT5 и VT6 становится весьма значительным. Большая часть напряжения питания +Епит выделяется на нагрузочных транзисторах, а с выхода снимается низкий уровень сигнала (логический 0).

Только когда на всех входах А, В и С присутствует низкий уровень сигнала (логический 0), управляющие транзисторы закрыты, а нагрузочные – открыты. Падение на нагрузочных транзисторах мало и они выполняют функцию стокового (нагрузочного) резистора Rс для параллельно включенных закрытых транзисторов VT1 ... VT3. С выхода снимается высокий уровень напряжения (логическая 1).

Таким образом, рассматриваемый элемент (рисунок 7.7) выполняет логическую функцию ИЛИ-НЕ

![]() .(7.1)

.(7.1)

Логические КМОП-элементы имеют ряд существенных достоинств. Во-первых, в статическом состоянии в цепи источника Епит находится запертый транзистор, так что потребляемая элементом мощность весьма мала. Потребление мощности происходит только при переключении элемента. Во-вторых, входное сопротивление полевого транзистора весьма велико, поэтому каждый последующий элемент практически не нагружает предыдущий. В-третьих, при исполнении по интегральной технологии полевой транзистор занимает на подложке (основании микросхемы) меньшую площадь, чем биполярный. Недостатком элемента является меньшее быстродействие, чем у ТТЛШ - и ЭСЛ - элементов.

При перевозке и монтаже КМОП-схем нужно соблюдать определенные меры предосторожности. В частности, монтажник и все монтажные инструменты должны быть заземлены, чтобы исключить возможность пробоя изоляции между затвором и каналом.

8. ГЕНЕРАТОРЫ ТАКТОВЫХ ИМПУЛЬСОВ (ГТИ) на логических элементах

8.1 ГТИ на двух инверторах

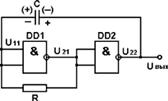

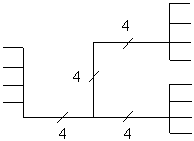

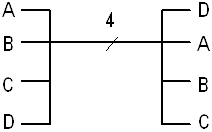

Существует много различных схем ГТИ (мультивибраторов) на логических элементах (ЛЭ) [6, 12], простейшей из которых является схема на двух элементах И-НЕ (инверторах) (рисунок 8.1).

Рисунок 8.1

Для стабилизации работы в схеме использована местная (охватывающая только одну ИМС) отрицательная обратная связь (ООС) через резистор R.

Необходимая для самовозбуждения генератора положительная обратная связь (ПОС) реализована через конденсатор С.

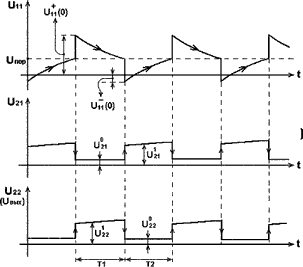

В процессе работы схемы перезаряд конденсатора С через резистор R (рисунок 8.2).

Рисунок 8.2

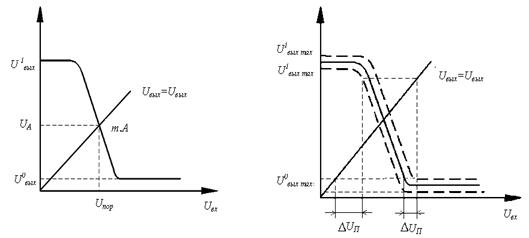

На временном интервале Т1 на входе элемента DD1 напряжение U11 > Uпор ≈ 1,3...1,5 В, где Uпор – пороговое напряжение логического элемента (рисунок 6.1). Поэтому на выходе DD1 поддерживается низкий уровень напряжения U021, а на выходе DD2 - высокий уровень U022. Ток перезаряда конденсатора течет от источника питания по цепи: (“+Епит”; R1вых2; С; R; R0вых1; “земля”) и экспоненциально уменьшается с постоянной времени

![]() .(8.1)

.(8.1)

При этом напряжение на входе DD1 также экспоненциально падает от начального напряжения ![]() , асимптотически стремясь к уровню

, асимптотически стремясь к уровню ![]() . В момент, когда напряжение на входе DD1 достигает уровня порога Uпор, инвертор DD1 переходит в усилительный режим (наклонный участок передаточной характеристики логического элемента (рисунок 6.1)). Напряжение U21 возрастает и инвертор DD2 также переходит в усилительный режим. В схеме начинает выполняться условие возникновения скачков: баланс амплитуд и баланс фаз (ПОС), что способствует быстрому (лавинообразному) переключению мультивибратора в другое квазиустойчивое состояние равновесия (U21 = 1, U22 = 0).

. В момент, когда напряжение на входе DD1 достигает уровня порога Uпор, инвертор DD1 переходит в усилительный режим (наклонный участок передаточной характеристики логического элемента (рисунок 6.1)). Напряжение U21 возрастает и инвертор DD2 также переходит в усилительный режим. В схеме начинает выполняться условие возникновения скачков: баланс амплитуд и баланс фаз (ПОС), что способствует быстрому (лавинообразному) переключению мультивибратора в другое квазиустойчивое состояние равновесия (U21 = 1, U22 = 0).

На выходе возникает отрицательный скачок напряжения, который через конденсатор С прикладывается ко входу U11, вызывая там тоже скачок напряжения. Т.к. ![]() , то на входе появляется небольшое отрицательное напряжение

, то на входе появляется небольшое отрицательное напряжение ![]() .

.

На временном интервале Т2 напряжение на входе DD1 U11 < Uпор, поэтому на выходе DD1 - высокий уровень ![]() , а на выходе элемента DD2 - низкий

, а на выходе элемента DD2 - низкий ![]() . Конденсатор С вновь перезаряжается. Ток перезаряда С протекает в противоположном направлении по цепи: (“+Епит”;

. Конденсатор С вновь перезаряжается. Ток перезаряда С протекает в противоположном направлении по цепи: (“+Епит”; ![]() ; R; С;

; R; С; ![]() ; “земля”).

; “земля”).

По мере перезаряда ток через резистор R уменьшается экспоненциально с постоянной времени

![]() ,(8.2)

,(8.2)

а напряжение на входе DD1 экспоненциально возрастает от уровня ![]() , асимптотически стремясь к уровню

, асимптотически стремясь к уровню ![]() .

.

В момент совпадения U11 и Uпор схема вновь переключается. На выходе U22 появляется положительный скачок напряжения, который через конденсатор С прикладывается ко входу U11, вызывая там также скачок напряжения. Далее описанные процессы повторяются.

Период генерируемых импульсов определяется зависимостью [12]

![]() (8.3)

(8.3)

при условии, что величина резистора R лежит в диапазоне:

Похожие работы

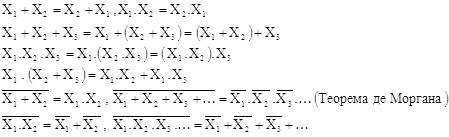

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

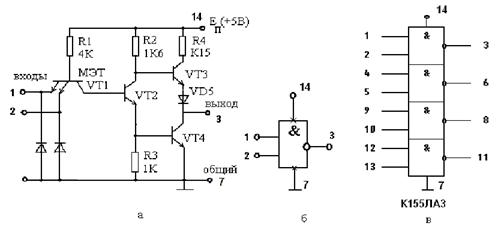

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

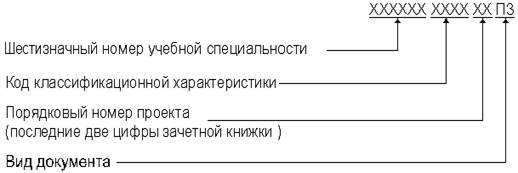

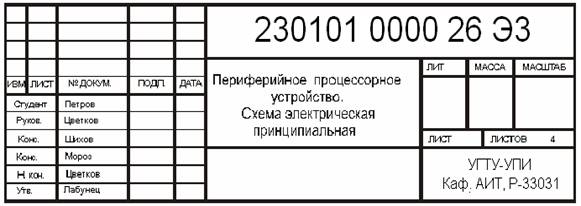

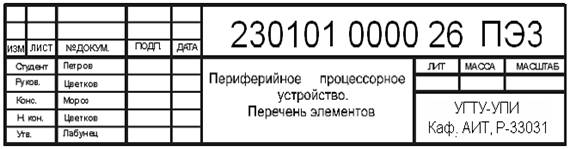

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев