Навигация

Синхронные RS - триггеры

9.2.1.1.1.2 Синхронные RS - триггеры

В результате явления “состязаний” (“гонок”) на входах асинхронного RS - триггера временно могут появляться ложные комбинации, которые вызовут ошибочные срабатывания (переключения) схемы и будут ложно зафиксированы логическим устройством обработки выходных сигналов триггера. Для устранения этого недостатка используют синхронные RS-триггеры, содержащие дополнительный тактовый (синхро) вход.

Синхронные RS - триггеры делятся на одноступенчатые (однотактные) и двухступенчатые (двухтактные).

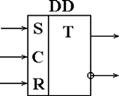

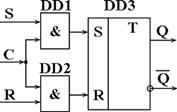

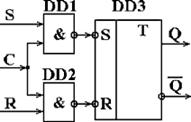

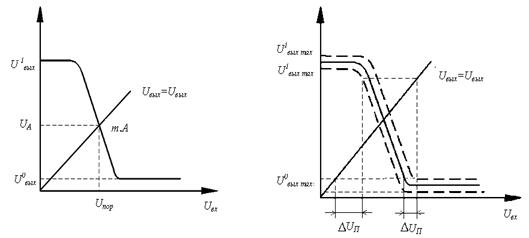

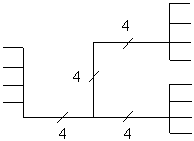

Ниже показаны: обозначение на электрических схемах (рисунок 9.31,а) и принципиальные схемы (рисунок 9.31, б, в) однотактного синхронного RS-триггера.

А Б

В

Рисунок 9.31

Однотактный синхронный RS-триггер (рисунок 9.31, б, в) включает асинхронный RS-триггер DD3 и два дополнительных логических элемента DD1, DD2: И (рисунок 9.31, б) или И-НЕ (рисунок 9.31, в). Более предпочтительной является вторая схема (рисунок 9.31, в), т.к. она содержит элементы одного базиса И-НЕ (см. рисунок 9.30).

Однотактный (одноступенчатый) синхронный RS-триггер (рисунок 9.31) тактируется (синхронизируется) потенциалом или единичным импульсом на входе С.

Часто нужно осуществлять переключение триггера перепадом потенциала на его синхровходе С из 1 в 0 или из 0 в 1 (срезом или фронтом входного импульса). Синхронный RS-триггер, обладающий такой способностью, называется двухступенчатым (двухтактным).

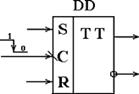

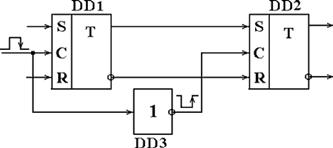

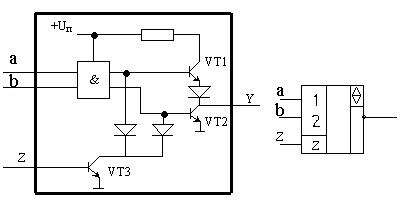

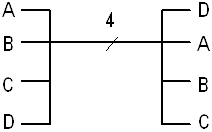

Ниже показаны: обозначение на электрических схемах (рисунок 9.32, а) и принципиальная схема (рисунок 9.32, б) двухтактного синхронного RS-триггера, переключающегося перепадом из 1 в 0 на динамическом тактовом (синхро) входе.

А Б

Рисунок 9.32

Триггер выполнен на двух однотактных синхронных RS-триггерах, рассмотренных выше, и инверторе DD3. Вход С (рисунок 9.32, а) называется динамическим, т.к. активным сигналом на нем является перепад из 1 в 0. Переключение триггера происходит за два такта: в первом такте входная информация записывается в первый триггер DD1, а состояние второго триггера DD2 не изменяется, т.к. на его синхровход с выхода инвертора подается нулевой импульс. Во втором такте в момент окончания единичного импульса на входе (при перепаде из 1 в 0) с выхода инвертора на синхровход триггера DD2 начинает поступать единичный потенциал и информация из первого триггера DD1 переписывается во второй DD2. Таким образом, состояние выхода меняется лишь в момент перепада из 1 в 0 входного синхросигнала.

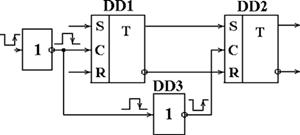

Ниже показаны: обозначение на электрических схемах (рисунок 9.33, а) и принципиальная схема (рисунок 9.33, б) двухтактного синхронного RS-триггера, переключающегося перепадом из 0 в 1 на динамическом синхровходе.

А Б

Рисунок 9.33

9.2.1.1.2 Т-триггеры (триггеры со счетным входом)

Такой триггер содержит счетный вход, обозначаемый буквой Т, и переключается каждым импульсом на этом входе (счетным импульсом).

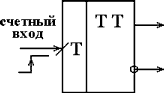

Ниже показаны: обозначение на электрических схемах (рисунок 9.34, а) и принципиальная схема (рисунок 9.34, в) Т-триггера, переключающегося перепадом из 1 в 0 каждого входного импульса.

А Б

В

Рисунок 9.34

Триггер выполнен на основе двухтактного синхронного двухступенчатого RSC-триггера с динамическим синхровходом, охваченного двумя обратными связями.

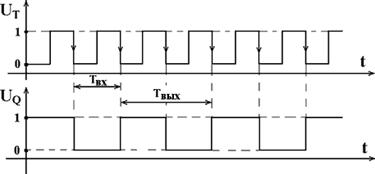

В момент среза счетных входных импульсов триггер переключается в противоположное состояние ![]() . На рисунке 9.35 приведены временные диаграммы, поясняющие работу Т-триггера. Исходное состояние схемы – единичное (UQ=1). Срезом каждого счетного импульса выходной сигнал меняет свое значение. Период выходных импульсов ТВЫХ = 2 ТВХ, а частота следования fВЫХ = fВХ/2, т.е. Т-триггер делит входную частоту на 2.

. На рисунке 9.35 приведены временные диаграммы, поясняющие работу Т-триггера. Исходное состояние схемы – единичное (UQ=1). Срезом каждого счетного импульса выходной сигнал меняет свое значение. Период выходных импульсов ТВЫХ = 2 ТВХ, а частота следования fВЫХ = fВХ/2, т.е. Т-триггер делит входную частоту на 2.

Рисунок 9.35

На рисунке 9.34, б приведено обозначение на электрических схемах Т-триггера, переключающегося перепадом из 1 в 0 на счетном входе.

Похожие работы

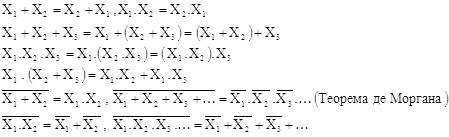

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

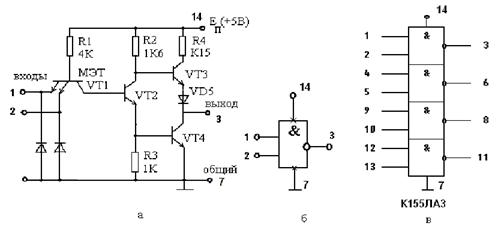

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

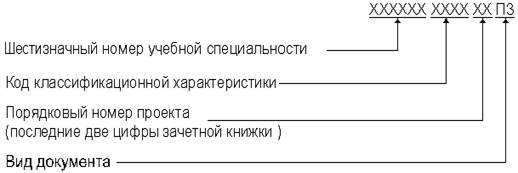

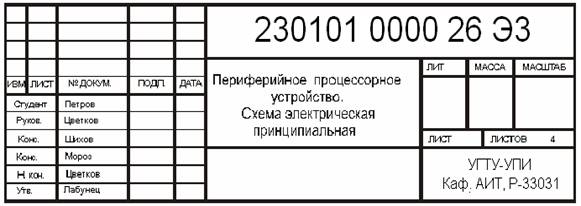

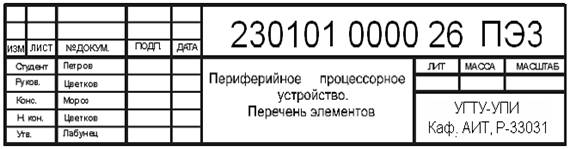

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев