Навигация

Допустимые значения основных параметров

6.10 Допустимые значения основных параметров

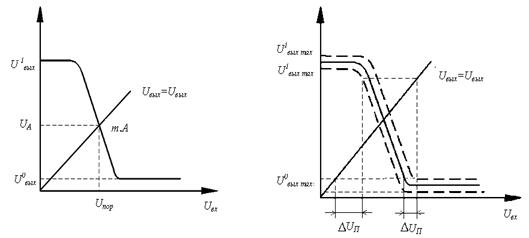

Emin, Emax – допустимые значения напряжения питания;

U1min, U0max – допустимые значения уровней логических сигналов единицы и нуля;

Iвх.max, I0вых.max, I1вых.min – допустимый входной и выходной токи в состоянии 0 и 1.

Существует еще ряд параметров, например, технико-экономических, которые приводятся в технической документации, прилагаемой к ИМС, и в справочниках.

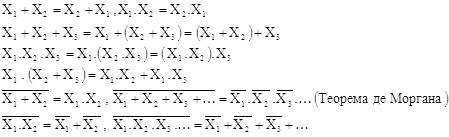

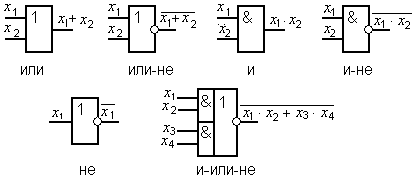

7. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Для построения цифровых устройств наиболее широкое применение находят интегральные логические элементы на базе ТТЛ -, ТТЛШ -, ЭСЛ - и КМОП - технологий. Всякая микросхема, реализующая сложную функцию, по существу представляет совокупность элементов И-НЕ или ИЛИ-НЕ.

7.1 Базовый ТТЛ (ТТЛШ) - элемент И-НЕ

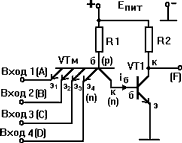

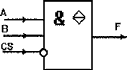

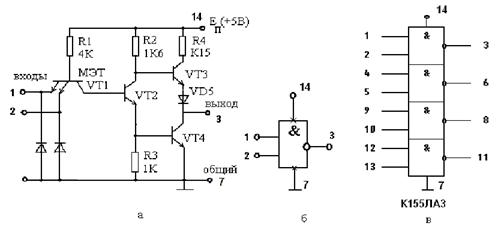

Простейший ТТЛ элемент, название которого расшифровывается как транзисторно-транзисторная логика, состоит из конъюнктора, выполненного на многоэмиттерном транзисторе VТм и транзисторного инвертора VT1 (рисунок 7.1).

Рисунок 7.1

При высоких уровнях напряжения на всех входах схемы (логические 1) все переходы эмиттер-база многоэмиттерного транзистора VTм смещаются в обратном направлении (заперты), а переход база-коллектор за счет напряжения +Епит – в прямом (инверсное включение транзистора). Ток коллекторного перехода транзистора VТм, протекающий через переход эмиттер-база транзистора VТ1, вводит последний в режим насыщения. При этом с выхода снимается низкий уровень напряжения (логический нуль). Если хотя бы на один вход схемы поступит сигнал логического 0(низкий уровень напряжения), VТм открывается и на базу VТ1 подается низкий уровень напряжения. Последний закрывается и с выхода снимается высокий уровень сигнала (логическая единица). Таким образом, элемент реализует функцию И-НЕ (![]() ).

).

Выходное сопротивление рассмотренного элемента зависит от состояния транзистора VТ1. Когда он открыт, оно близко к нулю, а когда заперт – Rвых≈Rк=R2.

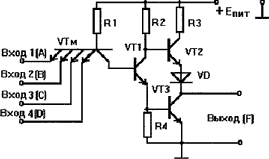

Для повышения помехоустойчивости и увеличения нагрузочной способности ТТЛ элементы содержат дополнительные транзисторы (рисунок 7.2).

Рисунок 7.2

Подобная схема называется ТТЛ элементом со сложным инвертором, выполненном на трех транзисторах VT1, VT2 и VT3. Если на всех входах элемента присутствует логическая 1, то эмиттерный переход VТм заперт, а коллекторный – открыт. Ток базы VТм через переход БКVTм поступает в базу VT1. В результате VT1 входит в режим насыщения. Положительным потенциалом, снимаемым с резистора R4, транзистор VT3 открывается и с выхода схемы снимается логический 0. Благодаря наличию диода VD транзистор VT2 при этом надежно закрыт.

Диод обеспечивает дополнительное положительное приращение напряжения на эмиттере VT2 и называется смещающим. Использование таких диодов – один из типовых приемов интегральной технологии, позволяющий обеспечить надежное запирание выключенных транзисторов. Наличие запертого VT2 в коллекторной цепи открытого VT3 практически исключает потребление тока выходной цепью сложного инвертора в состоянии покоя (без нагрузки). Нагрузка, включенная между +Епит и коллектором VT3 может вызывать достаточно большой ток (Iк.VT3=Iн).

Если хотя бы на один вход схемы (рисунок 7.2) поступит логический 0, то транзистор VТм насыщается, на его коллекторе (базе VT1) появляется низкий уровень напряжения и транзистор VT1 запирается. Потенциал его эмиттера стремится к нулю, а потенциал коллектора – к напряжению +Епит. Транзистор VT3 закрывается, VT2 – открывается. С выхода снимаем высокий уровень напряжения (логическая 1). Каскад на транзисторе VT2 работает в активном режиме как эмиттерный повторитель (значение резистора R3 мало (десятки Ом) и может не учитываться). Выходное сопротивление эмиттерного повторителя очень мало, поэтому нагрузочная способность второй схемы (рисунок 7.2) по сравнению с первой (рисунок 7.1) значительно увеличивается.

Потребление тока в выходной цепи ненагруженного сложного инвертора в этом состоянии также мало, так как VT3 закрыт. Если между выходом (коллектором VT3) и корпусом включить сопротивление нагрузки, то потребляемый схемой ток увеличивается (Iн=IэVT2).

Отсутствие собственного потребления тока выходной цепью сложного инвертора делает рассматриваемый элемент достаточно экономичным.

Вместе с тем, эта схема имеет существенный недостаток. При формировании логической единицы на выходе ток закрытого транзистора VT3 Iкоз протекает через резистор R4 (рисунок 7.2), создавая на нем падение напряжения, направленное на отпирание транзистора. Чтобы снизить это напряжение значение резистора R4 берется не очень большим (сотни Ом).

Малое значение R4 шунтирует переход база-эмиттер VT3 при его отпирании. Например, при напряжении Uбэ.нVT3=0,6 В через резистор R4=1 кОм протекает ток 0,6 мА. Следовательно, VT3 начнет отпираться только после того, как ток через резистор R4 возрастает до 0,6 мА. Это приводит к растягиванию во времени переходной области передаточной характеристики рассматриваемого элемента (рисунок 6.1).

Кроме того, наличие R4 влияет на стабильность параметров ТТЛ - элемента в рабочем диапазоне температур. Этот резистор имеет положительный температурный коэффициент сопротивления (ТКС). При возрастании температуры значение R4 увеличивается, его шунтирующее действие уменьшается, ток базы VT3 увеличивается, транзистор VT3 насыщается сильнее, что может увеличить время его выключения, т.е. ухудшает быстродействие. При снижении температуры значение R4 падает, его шунтирующее действие возрастает, что приводит к увеличению времени включения (растягиванию во времени переходной области передаточной характеристики микросхемы (рисунок 6.1)).

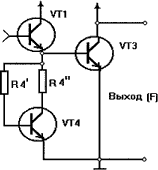

Для устранения отмеченных недостатков вместо резистора R4 в схему ТТЛ элемента включен нелинейный четырехполюсник (рисунок 7.3), выполненный на транзисторе VT4.

Это позволяет уменьшить длительность переходной области передаточной характеристики ТТЛ- элемента (рисунок 6.1) и повысить стабильность его параметров.

Рассмотренная схема со сложным инвертором также реализует функцию И-НЕ.

Рисунок 7.3

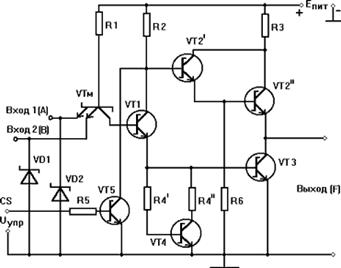

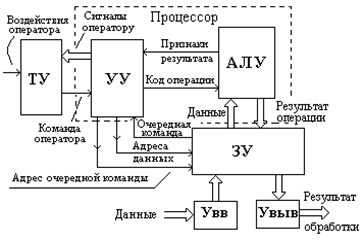

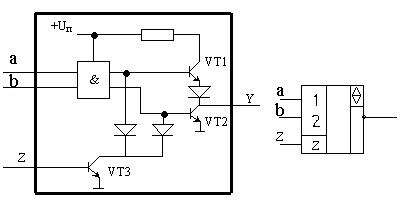

ТТЛ-схемы в настоящее время достаточно широко применяются в модифицированном ТТЛШ исполнении и содержат транзисторы и диоды Шоттки (рисунок 7.4).

Ниже показан пример двухвходового логического ТТЛШ - элемента И-НЕ (рисунок 7.4), имеющего ряд дополнительных элементов, отсутствующих в рассмотренной выше ТТЛ-схеме (рисунок 7.2).

Рисунок 7.4

Во-первых, для повышения нагрузочной способности вместо транзистора VТ2 (рисунок 7.2) в схему введен составной транзистор (VТ2′, VТ2″). Во-вторых, для защиты элемента от случайно поданных отрицательных входных сигналов в него включены диоды VD1, VD2. В-третьих, схема содержит транзистор VТ5, с помощью которого осуществляется перевод выхода схемы в третье, высокоимпедансное (Z) - состояние (см. 4.15). Положительный потенциал (логическая 1) на базе транзистора VТ5 открывает его, закорачивая тем самым коллектор транзистора VТ1 на землю.

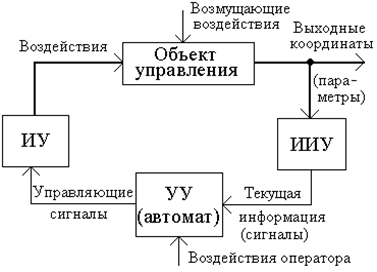

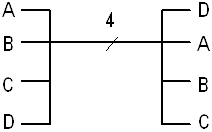

Это приводит к тому, что транзисторы VТ2′, VТ2″ и VТ3 остаются заперты, независимо от состояния входных управляющих сигналов. При этом выход F отключается как от шины питания, так и от земли, т.е. как бы повисает в воздухе. Функциональное обозначение такого логического элемента показано на рисунке 7.5.

Рисунок 7.5

Возможность перевода ТТЛ (ТТЛШ) схем в 3-е состояние позволяет использовать их при работе на одну системную шину, например, в микропроцессорных устройствах. При этом к общей шине подключен целый ряд различных устройств, снабженных выходными цепями с тремя состояниями, причем в каждый момент времени с общей шиной соединено только одно устройство, а выходы остальных находятся в 3-м (Z) - состоянии, т.е. отключены от шины.

Похожие работы

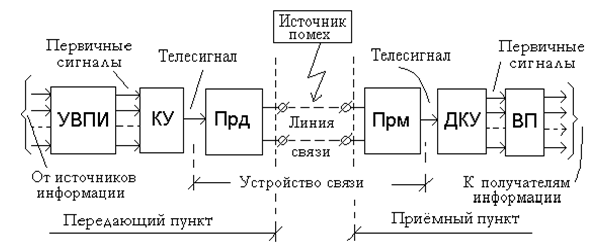

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

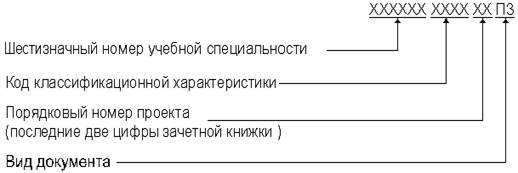

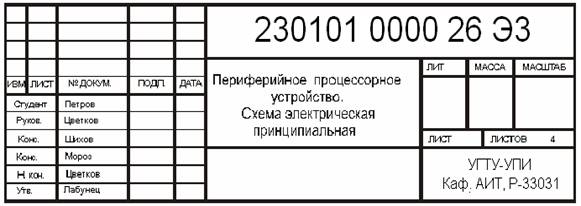

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев