Навигация

Запрет

4.13 Запрет

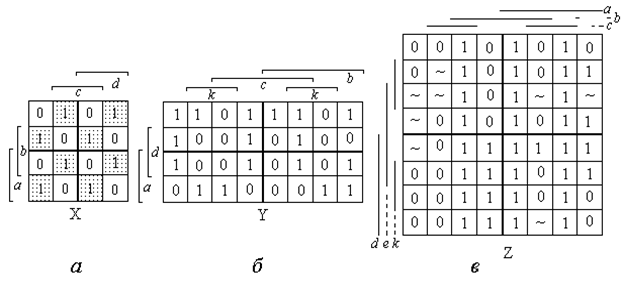

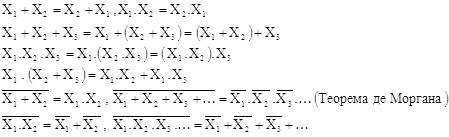

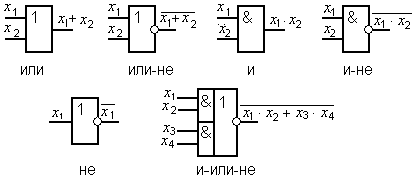

Элемент реализует логическую функцию

![]() .(4.13)

.(4.13)

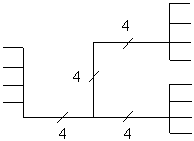

Ниже показаны его обозначение на электрических схемах (рисунок 4.14) и таблица истинности (таблица 4.12).

![]()

Рисунок 4.14

Таблица 4.12

| № набора | B | A | F |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 0 |

| 3 | 1 | 1 | 0 |

На выходе такого элемента логическая единица будет лишь в том случае, если на основном входе присутствует логическая единица (А=1), а на запрещающем входе– нуль (В=0)

В обозначении элемента на электрических схемах запрещающий вход отмечен как инверсный – кружком. Запрещающим сигналом на этом входе будет логическая единица.

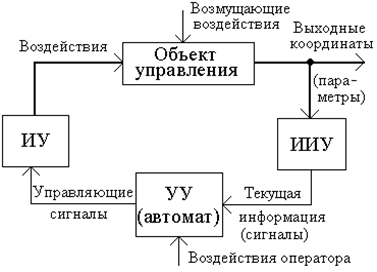

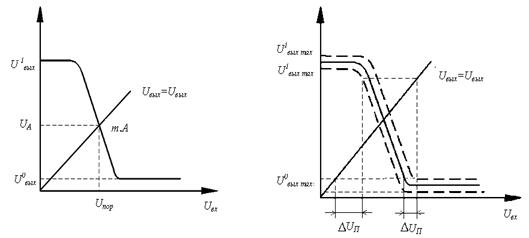

4.14 Логические элементы с открытым коллектором

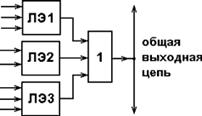

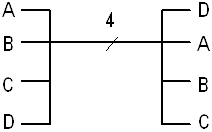

При построении цифровых устройств часто возникает необходимость объединения выходов нескольких логических элементов с целью перехода на общую выходную цепь. Эту задачу можно решить с помощью элемента ИЛИ (рисунок 4.15).

Рисунок 4.15

При этом приходится мириться с дополнительными схемными затратами и увеличением суммарной задержки прохождения цифровых сигналов через устройство.

Другой способ основан на применении логических элементов с открытым коллектором, в поле функционального обозначения которых имеется специальный символ ![]() , указывающий, что коллектор выходного транзистора открыт (оборван, “висит в воздухе”).

, указывающий, что коллектор выходного транзистора открыт (оборван, “висит в воздухе”).

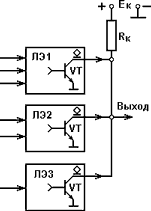

На рисунке 4.16 показано объединение нескольких логических элементов с открытым коллектором на общий выход.

Рисунок 4.16

Для нулевых сигналов на выходах логических элементов ЛЭ1...ЛЭ3 (соответствующий выходной транзистор открыт) данная схема выполняет функцию “монтажное ИЛИ”: при появлении логического нуля хотя бы на одном из выходов логических элементов выходной сигнал также будет равен нулю.

Для единичных сигналов на выходах логических элементов ЛЭ1...ЛЭ3 (соответствующий выходной транзистор закрыт) схема выполняет функцию “монтажное И”: выходной сигнал равен единице лишь при одновременном появлении логических единиц на выходах всех логических элементов.

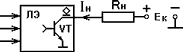

За счет технологии изготовления выходного транзистора и получения от него заданных характеристик элементы с открытым коллектором обладают более высокой нагрузочной способностью, чем обычные ЛЭ, поэтому могут использоваться для подключения нагрузок типа тиристоров, реле, индикаторов (светодиодов) и т.п. (рисунок 4.17).

Рисунок 4.17

При этом необходимо обеспечить выполнение условия

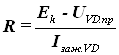

![]() ,(4.14)

,(4.14)

где Iн – ток нагрузки; ![]() – значение допустимого тока, который может протекать через открытый выходной транзистор логического элемента (рисунок 4.17).

– значение допустимого тока, который может протекать через открытый выходной транзистор логического элемента (рисунок 4.17).

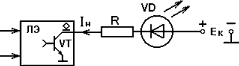

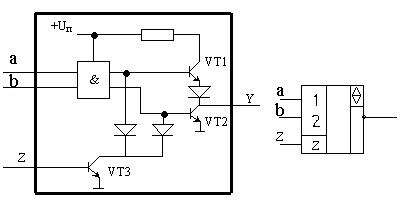

На рисунке 4.17.1 показан пример подключения на выход ЛЭ с открытым коллектором светодиода VD.

Рисунок 4.17.1

Когда с выхода ЛЭ снимается логический 0, выходной транзистор VT открыт, и светодиод VD оказывается включенным в прямом направлении. При протекании через VD прямого тока последний зажигается. Ток Iн равен току зажигания светодиода Iзаж.VD, который составляет £20 mA. Падение напряжения на открытом диоде UVD.пр составляет (1,7…2) В. Резистор R ограничивает величину прямого тока и рассчитывается по формуле:

(4.14.1)

(4.14.1)

Например, если Ek=5 B; UVD.пр=2 В; Iзаж.VD=20 mA, то R=(5-2)/(20*10-3)=150 Ом.

Похожие работы

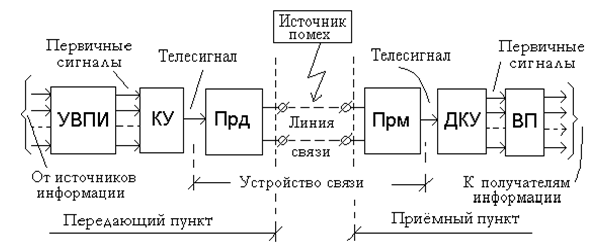

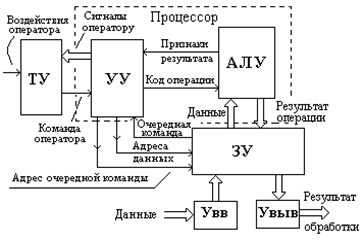

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

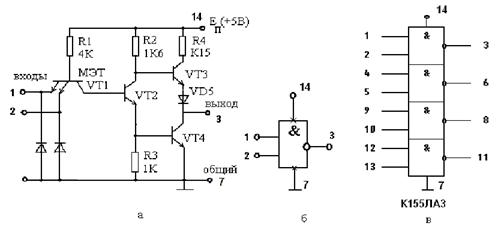

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

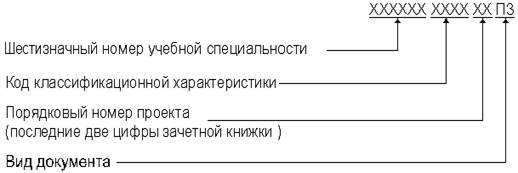

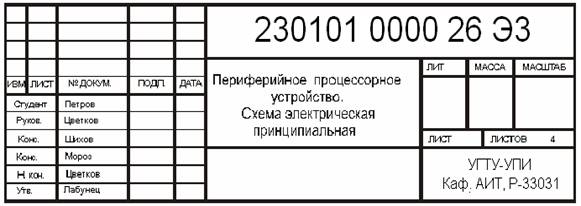

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев