Навигация

АЦП MAX154

10.2.4 АЦП MAX154

На современном рынке микросхем представлен широкий спектр СБИС АЦП, среди которых распространенными являются микросхемы фирмы «MAXIM».

Ниже рассмотрена одна из таких современных СБИС АЦП – MAX154, выполненная по КМОП технологии. Она представляет собой высокоскоростной четырехканальный АЦП, а также выполняет функции мультиплексора и УВХ.

10.2.4.1 Описание микросхемы MAX154. Временные диаграммы и режимы работы

Преобразователь имеет встроенное устройство выборки-хранения, мультиплексор, внутренний формирователь опорного напряжения: 2.5В.

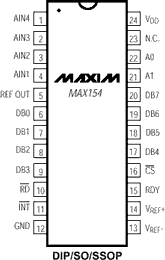

Рисунок 10.25

Диапазон аналогового входа: от 0В до 5В.

Питающее напряжение: +5В.

Время преобразования на каждый канал: 2.5 мкс.

Погрешность: 1/2 МЗР

Потребляемый входной ток: 15мA

Допустимый диапазон рабочих температур: от –40°С до +85°С.

Интерфейс с микропроцессором упрощен возможностью адресации микросхемы как области памяти или порта ввода/вывода без использования внешней логики. В качестве выхода используется регистр-защелка с третьим состоянием, что позволяет напрямую подключить микросхему к шине данных или портам ввода.

Внешний вид микросхемы приведен на рисунке 10.25, а описание выводов – в таблице 10.1.

Таблица 10.1 – Описание выводов микросхемы МАХ154

| Номер вывода | Наименование | Назначение |

| 1 | AIN4 | Аналоговый вход 4 |

| 2 | AIN3 | Аналоговый вход 3 |

| 3 | AIN2 | Аналоговый вход 2 |

| 4 | AIN1 | Аналоговый вход 1 |

| 5 | REF OUT | Выход внутреннего опорного напряжения: +2.5В |

| 6 | DBO | Бит 0 выхода |

| 7 | DB1 | Бит 1 выхода |

| 8 | DB2 | Бит 2 выхода |

| 9 | DB3 | Бит 3 выхода |

| 10 | RD | Управляющий бит доступа к данным и начала преобразования |

| 11 | INT | Сигнал индикации завершения преобразования |

| 12 | GND | Земля |

| 13 | Vref- | Нижняя граница входного сигнала |

| 14 | Vref+ | Верхняя граница входного сигнала |

| 15 | RDY | Выходной сигнал готовности для микро- процессора. Принимает значение логического нуля, когда CS активен, и переходит в третье состояние по окончанию преобразования. |

| 16 | CS | Выбор микросхемы (кристалла) |

| 17 | DB4 | Бит 4 выхода |

| 18 | DB5 | Бит 5 выхода |

| 19 | DB6 | Бит 6 выхода |

| 20 | DB7 | Бит 7 выхода |

| 21 | A1 | Бит 1 номера входного канала |

| 22 | A0 | Бит 0 номера входного канала |

| 23 | NC | Не подключен |

| 24 | Vdd | Питание +5В |

Таблица 10.2 отражает выбор входного канала адресными сигналами А1 и А0.

Таблица 10.2

| А1 | А0 | Входной канал |

| 0 | 0 | AIN1 |

| 0 | 1 | AIN2 |

| 1 | 0 | AIN3 |

| 1 | 1 | AIN4 |

Микросхема МАХ154 использует только два управляющих вывода: чтение - RD и выбор кристалла – CS. Операции чтения и преобразования инициируются низкими уровнями CS и RD, защелкивая адресные входы мультиплексора.

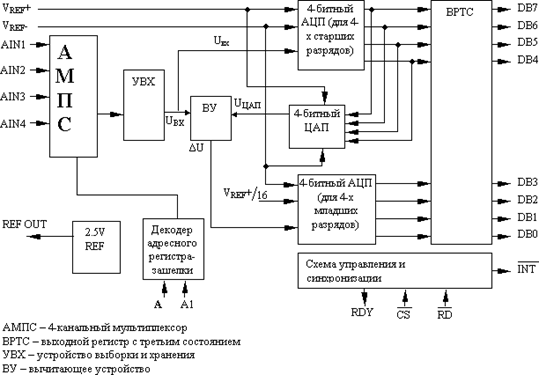

Функциональная схема MAX154 приведена на рисунке 10.26.

Рисунок 10.26

На входе схемы стоит четырехканальный аналоговый мультиплексор, который в зависимости от комбинации сигналов на адресных входах А0, А1 соединяет (коммутирует) один из аналоговых входов с устройством выборки-хранения, запоминающим входной сигнал и поддерживающим его практически неизменным в течении времени преобразования АЦП.

В АЦП использован «параллельно-последовательный» принцип преобразования. Два четырехразрядных параллельных АЦП служат для получения выходного 8-битного результата. Каждый из четырехразрядных АЦП содержит по пятнадцать компараторов, осуществляющих сравнение текущего значения входного сигнала с нормированными постоянными эталонными напряжениями. Величины этих напряжений зависят от значений опорных напряжений: VREF+ и VREF–, и отличаются друг от друга на величину Du, которая соответствует изменению выходного 4-разрядного ДК каждого АЦП на ±1мзр.

Вначале преобразования, используя 15 компараторов, верхний 4-битный АЦП старших 4-х разрядов сравнивает неизвестное входное напряжение с эталонными напряжениями и подает на выход 4-ре старших бита. Одновременно эти значения старших бит поступают на вход ЦАП, который формирует аналоговое напряжение, пропорциональное этому коду. Это напряжение вычитается из входного аналогового сигнала и полученная разность Du поступает на вход нижнего 4-битного АЦП, где сравнивается с эталонными напряжениями 15 компараторов для получения значений 4-х младших разрядов выходного ДК. На выходе MAX154 находится регистр-защелка с третьим состоянием, что позволяет напрямую подключать микросхему к шине данных или портам ввода.

Описание работы параллельного 4-х разрядного АЦП

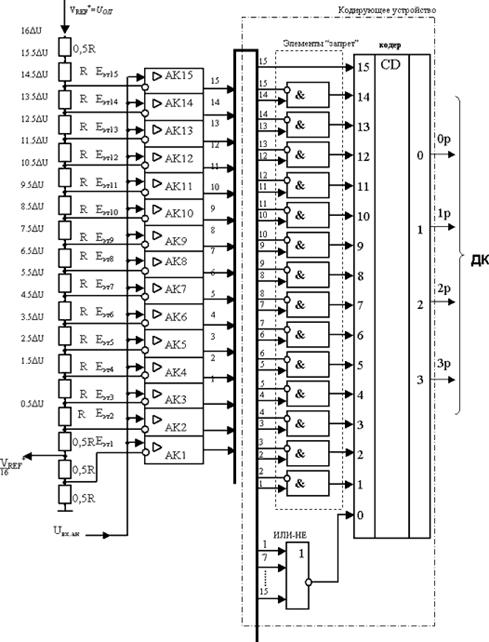

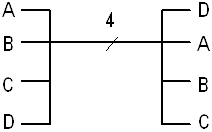

Простейшая схема четырехразрядного АЦП дана на рисунке 10.26.1.

Рисунок 10.26.1

Преобразователи этого типа осуществляют одновременное квантование сигнала с помощью набора компараторов, включенных параллельно источнику входного сигнала. Пороговые уровни компараторов устанавливаются с помощью резистивного делителя, подключенного к источнику опорного напряжения UОП в соответствии с используемой шкалой квантования. Число уровней квантования, а соответственно и число компараторов для n-разрядного АЦП равно 2n-1.

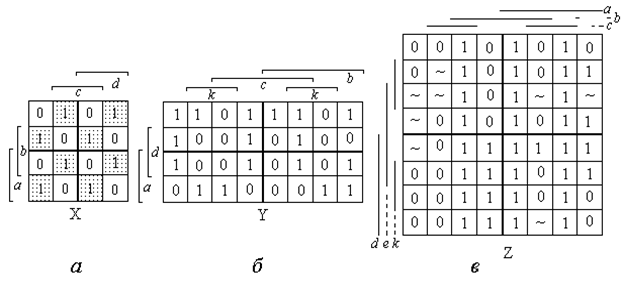

При подаче на такой набор компараторов сигнала UВХ на их выходах имеет место дискретный сигнал, отображающий срабатывание отдельных компараторов. Так, например (см. рисунок 10.26.1) если входное напряжение не выходит за пределы диапазона от 2,5Du до 3,5Du (Du – шаг квантования), то компараторы с первого по третий устанавливаются в состояние 1, а компараторы с четвертого по пятнадцатый – в состояние 0. Для преобразования числа сработавших компараторов в двоичный код используется соответствующее кодирующее устройство. Состояния данного кодирующего устройства для четырехразрядного АЦП показаны в таблице 10.2.1

Таблица 10.2.1

| Входное напряжеие | Состояние компараторов | Выходной двоичный код | |||||||||||||||||

| u*вх | К15 | К14 | K13 | K12 | K11 | K10 | K9 | K8 | K7 | K6 | K5 | K4 | K3 | K2 | K1 | а3 | а2 | а1 | а0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 4 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 5 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 6 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

| 7 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 8 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 9 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 10 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 11 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 12 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 13 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 14 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 15 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

*Входное напряжение дано в условных единицах: цифрами от 0 до 15 пронумерованы уровни квантования аналогового входного сигнала.

Кодирующее устройство (рисунок 10.26.1) реализовано с применением одного 15-ти входового логического элемента “ИЛИ-НЕ”; 14-ти элементов “запрет” и шифратора (преобразователя) 16-позиционного ”унитарного” кода в 4-х разрядный двоичный код.

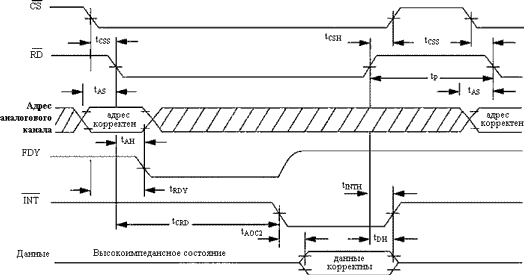

Существует два режима работы микросхемы, которые определяются длительностью сигнала на входе RD.

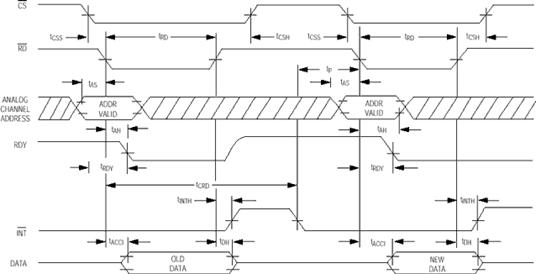

Режим 0 (рисунок 10.27) инициализируется удержанием низкого значения сигнала чтения RD до завершения преобразования.

Рисунок 10.27

Он предназначен для микропроцессоров, которые могут быть переведены в состояние ожидания. В этом режиме преобразование начинается вместе с операцией чтения (низкий уровень CS и RD), и данные считываются, когда преобразование завершается. Логический ноль на входах CS и RD защелкивает адресные входы мультиплексора и инициирует преобразование. Выходы DB0-DB7 находятся в высокоимпедансном состоянии до окончания преобразования. Сигнал готовности RDY подключается ко входу READY/WAIT микропроцессора. RDY принимает логический ноль по спаду CS и переходит в высокоимпедансное состояние по окончанию преобразования, когда результат выдается на линии данных. Сигнал INT принимает значение логического нуля, когда преобразование заканчивается и логической единицы, когда сигнал на входе RD переходит в единичное состояние. Режим 1 (рисунок 10.28) не требует ожидания со стороны микропроцессора.

Рисунок 10.28

Операция чтения одновременно инициирует преобразование и чтение результатов предыдущего преобразования. Сигнал INT принимает значение логической единицы по фронту RD и логического нуля по окончанию преобразования. Вторая операция чтения необходима для считывания результатов предыдущего преобразования. Второй сигнал RD защелкивает новый адрес в мультиплексоре и инициирует следующее преобразование. Задержка в 2,5мкс должна соблюдаться между операциями чтения.

В нашем случае будем использовать режим работы 0, т.к. режим 1 требует длительность сигнала ![]() £600нс. Для выбранной ОМЭВМ эта длительность равна 1 мкс.

£600нс. Для выбранной ОМЭВМ эта длительность равна 1 мкс.

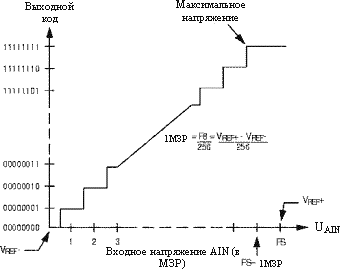

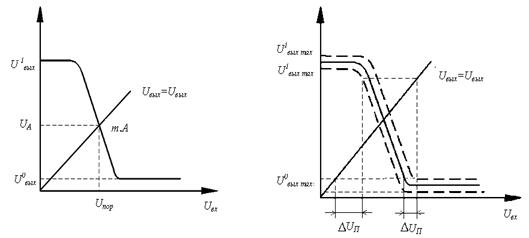

На рисунке 10.29 приведена передаточная характеристика MAX154.

Рисунок 10.29

Похожие работы

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

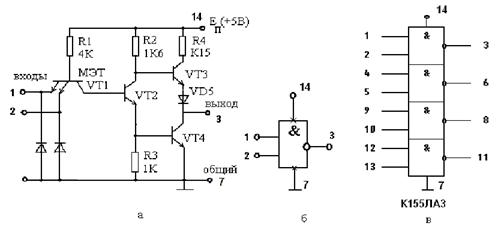

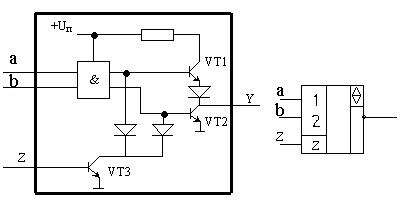

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

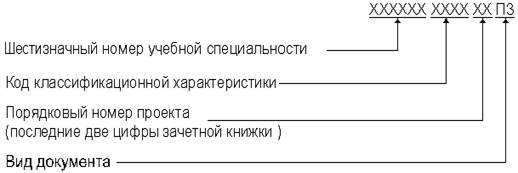

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев