Навигация

D-триггеры (триггеры задержки)

9.2.1.1.3 D-триггеры (триггеры задержки)

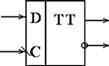

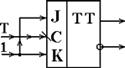

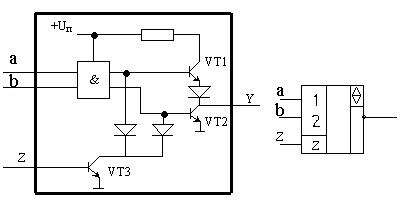

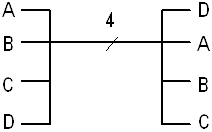

Содержат информационный (D) вход и тактовый (синхро, С) вход (рисунок 9.36).

А Б

Рисунок 9.36

Существуют однотактные D-триггеры (рисунок 9.36, а), которые переключаются потенциалом или импульсом на тактовом входе, и двухтактные D-триггеры, которые переключаются динамическим сигналом (перепадом), например, из 1 в 0 (рисунок 9.36, б).

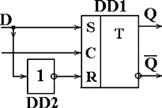

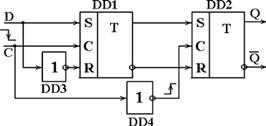

Ниже показаны: принципиальная схема (рисунок 9.37, а) и временные диаграммы работы (рисунок 9.37, б) однотактного D-триггера, выполненного на однотактном синхронном RS-триггере (RSC-триггере - DD1) и логическом элементе DD2.

А Б

Рисунок 9.37

В момент прихода тактового импульса D-триггер переключается в состояние, определяемое сигналом на информационном входе D, т.е. схема запоминает сигнал на входе D в момент поступления синхроимпульса (Qt+1 = D) и хранит его до следующего тактового импульса. Задержка равна интервалу времени между моментами прихода информационного сигнала на D-вход и поступлением синхросигнала на С-вход: tзад1 = t2 - t1; tзад2 = t4 - t3 (рисунок 9.37, б). D-триггеры широко применяются в качестве элементов памяти, способных хранить 1 бит информации.

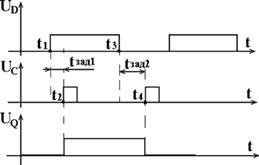

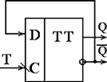

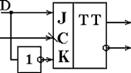

Ниже показаны: обозначение на электрических схемах (рисунок 9.38, а) и принципиальная схема (рисунок 9.38, б) двухтактного D-триггера, переключающегося перепадом из 1 в 0 на динамическом синхровходе С.

А Б

В

Рисунок 9.38

Триггер выполнен на основе двух однотактных RSC-триггеров (DD1, DD2) и двух инверторов (DD3, DD4).

D-триггер можно использовать в качестве триггера со счетным входом (Т-триггера), если соединить его выводы как показано на рисунке 9.38, в.

9.2.1.1.4 JK-триггеры

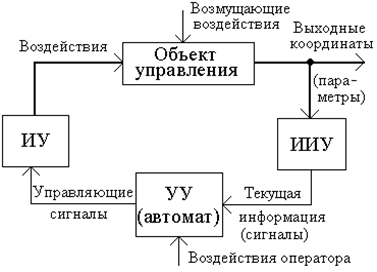

Является наиболее универсальным среди синхронных триггеров.

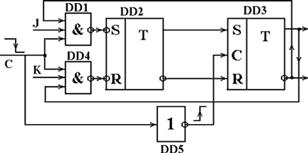

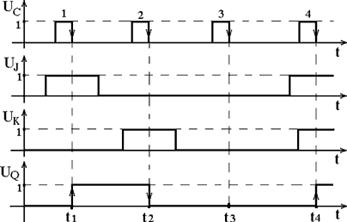

Ниже показаны: обозначение на электрических схемах (рисунок 9.40, а), принципиальная схема (рисунок 9.40, б), таблица истинности (таблица 9.13) и временные диаграммы работы (рисунок 9.40, в) двухтактного синхронного JK-триггера, переключающегося перепадом из 1 в 0 на динамическом синхровходе С.

А Б

В

Рисунок 9.40

Таблица 9.13

| № набора | J | K | C | Qt+1 |

| 0 | 0 | 0 |

| Qt |

| 1 | 0 | 1 |

| 0 |

| 2 | 1 | 0 |

| 1 |

| 3 | 1 | 1 |

|

|

Рассмотрим работу JK-триггера. Исходное состояние схемы - нулевое (UQ = 0) (рисунок 9.40, в). При поступлении среза первого тактового импульса (момент t1) сигнал на J-входе равен 1, а на К-входе - 0. Поэтому триггер переключается в единичное состояние. Срезом второго тактового импульса схема переключается в нулевое состояние (момент t2), т.к. в это время J=0, а К=1. В момент t3 оба управляющих сигнала J=K=0, поэтому состояние схемы не изменяется (Qt+1 = Qt). При поступлении среза 4-го синхроимпульса (момент t4) J=K=1, поэтому триггер переключается в положение, противоположное исходному: ![]()

На основе универсального JK-триггера может быть построен ряд других триггеров.

Синхронный RS-триггер. Отождествим J=S и K=R. При запрете комбинации J=S=1 и K=R=1 таблица 9.13 сводится к таблице истинности RS-триггера (таблица 9.11). Поэтому рассмотренная схема (рисунок 9.40) может использоваться в качестве двухтактного синхронного RS-триггера.

Счетный Т-триггер. В нем используется только 4-я строка таблицы 9.13. Для этого входы J и K присоединяются к потенциалу, соответствующему логической единице: J=K=1 (рисунок 9.41, а).

А Б

Рисунок 9.41

D-триггер. В этом триггере ![]() , т.е. помимо тактового имеется только один вход D (рисунок 9.41, б). Из таблицы 9.13 (2-я и 3-я строки) видно, что в D-триггере Qt+1 = D, т.е. последний запоминает сигнал на входе D в момент среза тактового импульса и хранит его до следующего синхросигнала.

, т.е. помимо тактового имеется только один вход D (рисунок 9.41, б). Из таблицы 9.13 (2-я и 3-я строки) видно, что в D-триггере Qt+1 = D, т.е. последний запоминает сигнал на входе D в момент среза тактового импульса и хранит его до следующего синхросигнала.

Похожие работы

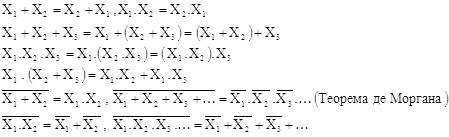

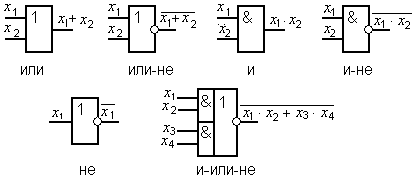

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

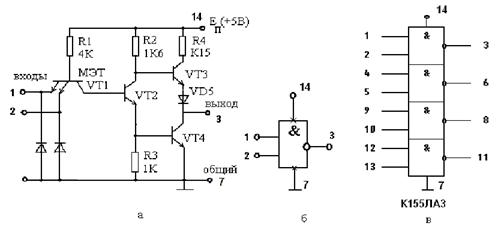

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

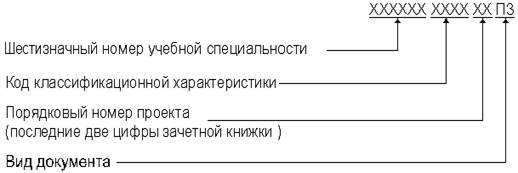

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев