Навигация

Реализация логических функций в различных базисах

5.2 Реализация логических функций в различных базисах

5.2.1 Реализация элемента “Равнозначность” (исключающее ИЛИ - НЕ)

На выходе такого элемента должна быть логическая 1, если на входах одновременно присутствуют одинаковые логические переменные (единицы или нули).

Булево выражение логической функции, соответствующей рассматриваемому элементу имеет вид

![]() .(5.1)

.(5.1)

Очевидно, что данное выражение легко реализуется элементами базиса И, ИЛИ, НЕ.

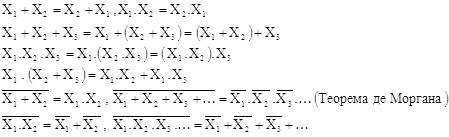

Используя теорему де Моргана и тождества булевой алгебры, преобразуем выражение (5.1) к виду, позволяющему реализовать функцию “равнозначность” в базисе И-НЕ (5.2) и ИЛИ-НЕ (5.3)

![]() ,(5.2)

,(5.2)

![]() .(5.3)

.(5.3)

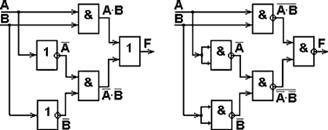

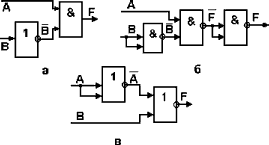

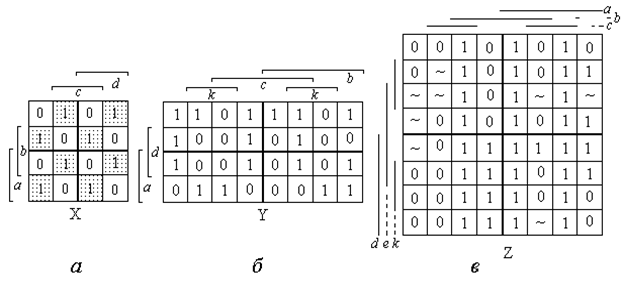

Ниже показаны функциональные схемы элемента “равнозначность” на ЛЭ базисов И, ИЛИ, НЕ (рисунок 5.2,а); И-НЕ (рисунок 5.2,б) и ИЛИ-НЕ (рисунок 5.2,в).

А Б

В

Рисунок 5.2

5.2.2 Реализация элемента “Неравнозначность” (исключающее ИЛИ, сумма по модулю два)

На выходе такого элемента должна быть логическая 1, если на входах присутствуют неравнозначные логические переменные:

F = 1, если А = 1, В = 0 или А = 0, В = 1.

Булево выражение логической функции рассматриваемого элемента имеет вид

![]() .(5.4)

.(5.4)

Это выражение может быть легко реализовано элементами базиса И, ИЛИ, НЕ. Применяя теорему де Моргана и тождества булевой алгебры, преобразуем выражение (5.4) к виду, позволяющему реализовать функцию “неравнозначность” в базисе И-НЕ (5.5) и ИЛИ-НЕ (5.6).

![]() ,(5.5)

,(5.5)

![]() .(5.6)

.(5.6)

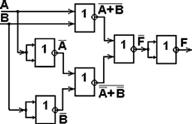

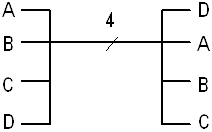

Ниже показаны функциональные схемы элемента “неравнозначность” на ЛЭ базисов И, ИЛИ, НЕ (рисунок 5.3, а); И-НЕ (рисунок 5.3, б) и ИЛИ-НЕ (рисунок 5.3, в).

А Б

В

Рисунок 5.3

Элемент “неравнозначность” иначе называют сумматором по модулю два: сумма двоичных цифр дает единицу, если одна из них единица, а другая – нуль; в противном случае, если обе цифры 0 или 1, то сумма равна нулю.

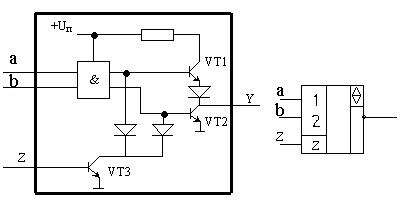

5.2.3 Реализация элемента “Запрет”

На выходе такого элемента должна быть логическая 1, если на основном входе присутствует логическая единица, а на запрещающем входе – логический нуль.

Булево выражение логической функции рассматриваемого элемента имеет вид

![]() .(5.7)

.(5.7)

Выражение (5.7) может быть легко реализовано в базисе И, ИЛИ, НЕ.

Применяя теорему де Моргана и тождества булевой алгебры, преобразуем выражение (5.7) к виду, позволяющему реализовать функцию “запрет” в базисе И-НЕ (5.8) и ИЛИ-НЕ (5.9).

![]() ,(5.8)

,(5.8)

![]() .(5.9)

.(5.9)

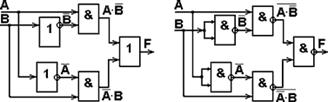

Ниже показаны функциональные схемы элемента “запрет” на ЛЭ базисов И, ИЛИ, НЕ (рисунок 5.4, а); И-НЕ (рисунок 5.4, б) и ИЛИ-НЕ (рисунок 5.4, в).

Рисунок 5.4

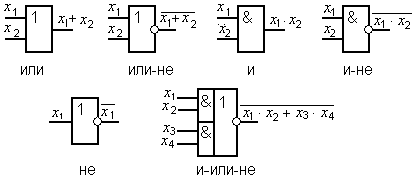

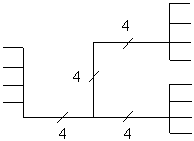

5.2.4 Реализация многобуквенных логических функций на элементах с небольшим количеством входов

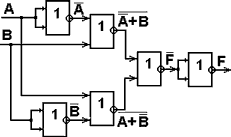

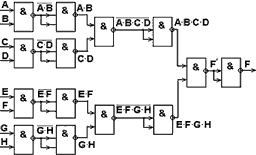

Иногда на практике возникает задача реализовать логическую функцию большого числа логических переменных (многобуквенную функцию) на элементах с небольшим количеством входов. В качестве примера на рисунке 5.5 показана функциональная схема, реализующая логическую функцию

![]() (5.10)

(5.10)

на двухвходовых элементах И-НЕ.

Рисунок 5.5

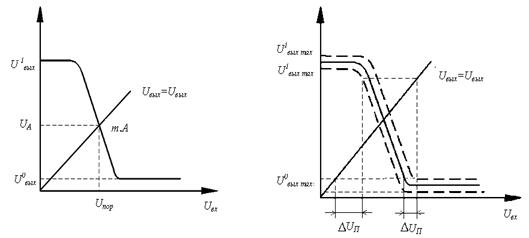

6. ПАРАМЕТРЫ И ХАРАКТЕРИСТИКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ (ИМС)

Цифровая микросхема как функциональный узел характеризуется набором сигналов, которые можно разделить на информационные (Х1, Х2, ..., Хn – входные, Y1, Y1, ..., Ym – выходные) и управляющие (V1, V2, ..., Vk). Каждая конкретная ИМС в соответствии со своим функциональным назначением выполняет определенные операции над входными сигналами (переменными), а выходные сигналы представляют собой результат этих операций Yj = F(Х1,Х2, ... ,Хn). Операторами F могут быть как простейшие логические преобразования, например, И, ИЛИ, НЕ, и т. д., так и сложные многофункциональные преобразования, имеющие место, например, в микропроцессорах, БИС памяти и др.

Сигналы управления определяют вид операции, режим работы ИМС, обеспечивают синхронизацию, установку начального состояния, стробируют входные и выходные сигналы, задают адрес, и т. д.

От функциональной сложности ИМС зависит и система ее электрических параметров, которые в общем случае могут иметь десятки наименований, причем многие из параметров характерны только для ИМС какого-либо одного класса. Поэтому ниже рассмотрим те параметры и характеристики, которые характеризуют большинство микросхем. В дальнейшем при изучении отдельных устройств этот перечень по мере необходимости будет расширен.

6.1 Коэффициент объединения по входу (Коб)

Равен числу входов логического элемента. На них поступают логические переменные, над которыми данный элемент выполняет логическую операцию. Коб ограничивает наибольшее число переменных функции, которую реализует данный ЛЭ. При недостаточном количестве входов вместо одного приходится использовать несколько элементов, соединяя их определенным образом (5.2.4).

Похожие работы

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

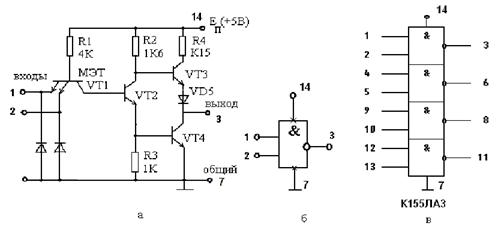

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев