Навигация

Демультиплексоры

9.1.2.2.2 Демультиплексоры

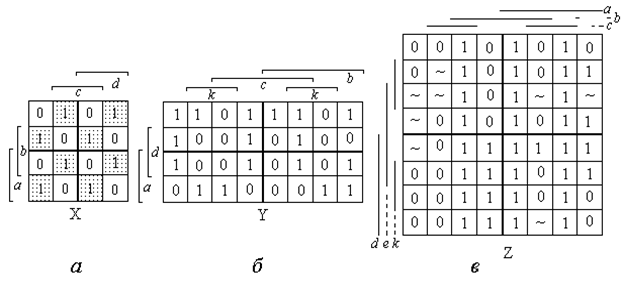

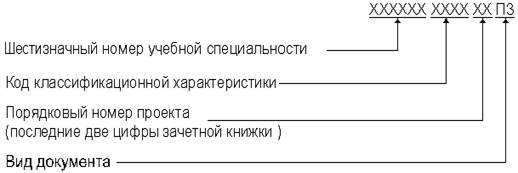

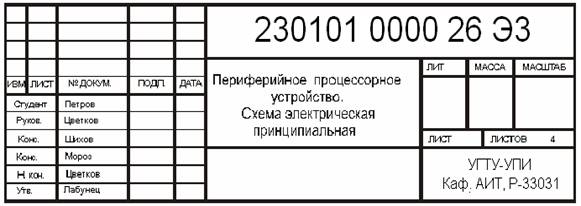

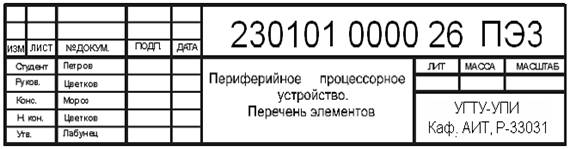

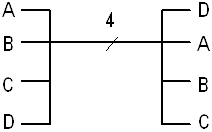

Демультиплексор – это КЦУ, которое соединяет (коммутирует) общий информационный вход с одним из нескольких выходов в соответствии с заданным кодом на управляющих (адресных) входах. Иными словами, демультиплексоры решают задачи, обратные мультиплексированию. Пример обозначения демультиплексора на электрических схемах показан на рисунке 9.16, a.

Схема имеет четыре информационных выхода и два адресных входа А0 и А1. Булевы выражения, описывающие работу данного демультиплексора, имеют вид:

(9.7)

(9.7)

Такими же выражениями определяется работа дешифратора с синхровходом V (рисунок 9.16, б). Поэтому его можно использовать в качестве демультиплексора, если информационный входной сигнал подавать на вход V.

А Б

Рисунок 9.16

9.1.2.2.3 Мультиплексоры–селекторы (мультиплексоры-демультиплексоры)

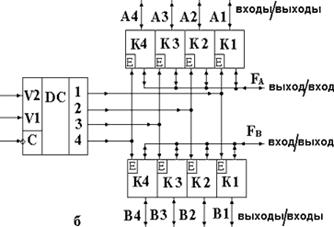

Мультиплексоры – селекторы являются двунаправленными, поскольку позволяют коммутировать цифровые и аналоговые сигналы в обоих направлениях, и поэтому могут быть использованы не только в качестве мультиплексора для коммутации одного из входов на выход, но и в качестве селектора (демультиплексора) для коммутации входа на один из выходов.

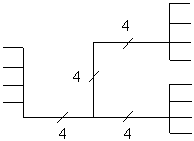

Ниже показаны: обозначение мультиплексора-селектора (демультиплексора) на электрических схемах (рисунок 9.17, а) и его упрощенная внутренняя структура (рисунок 9.17, б).

Рисунок 9.17

Устройство содержит две группы двунаправленных ключей (К1...К4) и дешифратор. Выходные сигналы дешифратора воздействуют на управляющие входы ключей (Е) и определяют их состояние. При Е=0 ключ закрыт, а при Е=1 – открыт и образует низкоомную цепь распространения сигнала через него. Такой ключ называют аналоговым, поскольку он обеспечивает неискаженную двухстороннюю передачу сигналов. Каждый ключ К имеет два равнозначных вывода, любой из которых может быть входом или выходом. По одному из выводов ключи объединены в две группы FА и FВ, которые образуют выходы мультиплексоров и входы демультиплексоров.

Структуру, представленную на рисунке 9.17, б, имеет микросхема К561(564)КП1, выполненная по КМОП-технологии и содержащая два мультиплексора - селектора, управляемые от общих входов V1, V2 и С (рисунок 9.17, а). При единичном управляющем сигнале на входе С ключи разомкнуты и выходы находятся в 3-м состоянии.

9.1.2.3 Сумматоры и полусумматоры

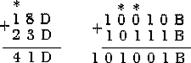

Сумматор предназначен для сложения двух чисел, заданных в двоичном коде. Из примера, приведенного на рисунке 9.18, видно, что правила сложения десятичных и двоичных чисел одинаковы:

1) сложение производится поразрядно от младшего разряда к старшему;

2) сумма младших разрядов слагаемых А0 и В0 записывается в соответствующей системе счисления однозначным числом S0 либо двухзначным числом P0S0, где Р0 называется переносом из нулевого разряда в соседний первый;

3) во всех последующих разрядах находится сумма данных разрядов слагаемых Ai, Bi и переноса Pi-1 от сложения предыдущих разрядов (в примерах на рисунке 9.18 этот случай помечен звездочкой).

Рисунок 9.18

Cказанное отражает таблица истинности одноразрядного двоичного полного сумматора (таблица 9.6).

Таблица 9.6

| N набора | Аi | Bi | Pi-1 | Si | Pi |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 2 | 0 | 1 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 | 0 | 1 |

| 4 | 1 | 0 | 0 | 1 | 0 |

| 5 | 1 | 0 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 | 1 |

Булевы выражения логических функций Si и Pi в СДНФ имеют вид

![]() ,(9.8)

,(9.8)

![]() .(9.9)

.(9.9)

Выражение (9.9) можно минимизировать. В результате получим

![]() .(9.10)

.(9.10)

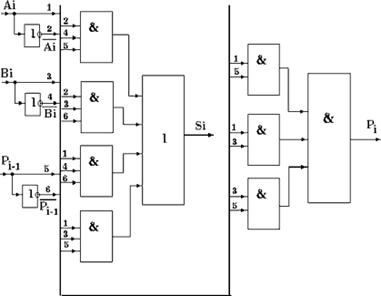

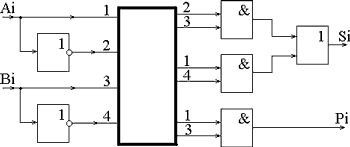

На основании выражений (9.8, 9.10) одноразрядный двоичный полный сумматор может быть реализован в базисе И, ИЛИ, НЕ (рисунок 9.19).

Рисунок 9.19

Используя правила перехода из базиса И, ИЛИ, НЕ в базис И-НЕ и ИЛИ-НЕ (5.1), можно построить одноразрядный полный сумматор в двух других базисах.

Обозначение одноразрядного сумматора на электрических схемах приведено на рисунке 9.20, в.

Полусумматор, в отличие от полного сумматора, обеспечивает выполнение операции суммирования двух одноразрядных двоичных чисел Ai и Bi без учета сигнала переноса. В результате сложения наряду с суммой может получиться перенос. Функционирование полусумматора описывается таблица 9.7.

Таблица 9.7

| N набора | Аi | Bi | Si | Pi |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 2 | 1 | 0 | 1 | 0 |

| 3 | 1 | 1 | 0 | 1 |

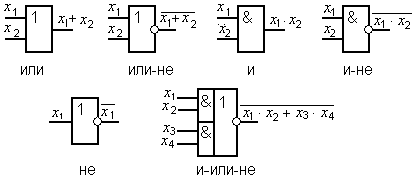

Пример проектирования полусумматора на логических элементах.

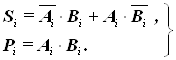

Как видно из таблицы 9.7, для реализации функции Si необходим элемент “неравнозначность” (сумматор по модулю два), а для реализации функции Pi - логическое И. Булевы выражения для Si и Pi в СДНФ имеют вид:

.(9.11)

.(9.11)

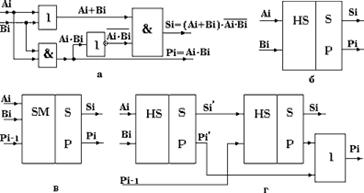

На рисунке 9.20.1 приведена схема, реализующая выражение 9.11 на элементах И, ИЛИ, НЕ.

Рисунок 9.20.1

Для получения более простой схемы одноразрядного полусумматора на логических элементах функцию Si лучше представить в СКНФ (см. таблицу 9.7)

![]() .(9.12)

.(9.12)

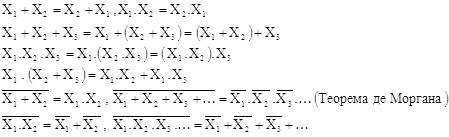

Выполнив преобразование по теореме де Моргана, получим:

![]() ,(9.13)

,(9.13)

где Ai∙Bi = Pi (см. 9.11).

Выражение (9.13) реализуется схемой, показанной на рисунке 9.20, а.

Рисунок 9.20

Если сравнить эту схему со схемой, реализующей выражение (9.11), то схема на рисунке 9.20, а выглядит проще.

Условные графические обозначения полусумматора и полного одноразрядного сумматора на электрических схемах показаны на рисунке 9.20 б, в, а схема полного одноразрядного сумматора, выполненного на двух полусумматорах, показана на рисунке 9.20, г.

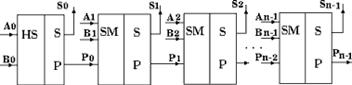

Для сложения n-разрядных чисел необходимо (n-1) одноразрядных полных сумматоров и один полусумматор в нулевом разряде (рисунок 9.21).

В этом сумматоре реализована последовательная передача переноса из одного разряда в другой. При большом количестве разрядов суммируемых чисел длительность суммирования в сумматорах с последовательным переносом может оказаться недопустимо большой. Бóльшим быстродействием обладают сумматоры с параллельным переносом, содержащие схему ускоренного переноса [3].

Рисунок 9.21

Похожие работы

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

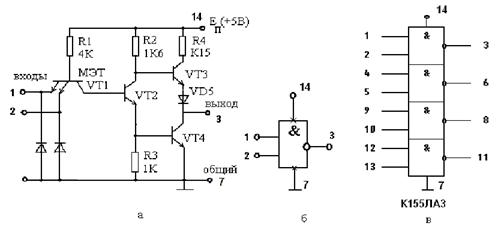

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев