Навигация

Построение КЦУ на дешифраторах

9.1.3.2 Построение КЦУ на дешифраторах

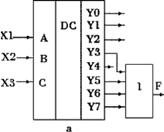

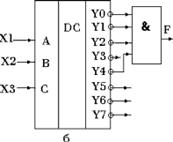

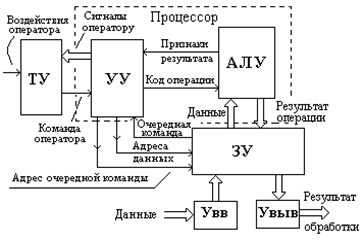

Для построения КЦУ можно использовать дешифраторы. Так как активное значение сигнала на каждом выходе дешифратора определяет одну из комбинаций входных сигналов, то, объединяя с помощью соответствующих логических элементов некоторые выходные сигналы дешифратора, можно реализовать КЦУ, заданное любой таблицей истинности, с числом наборов, не превышающим число выходов используемого дешифратора.

Рассмотрим пример реализации трехвходового мажоритарного элемента (таблица 9.8) на трехвходовом дешифраторе.

Для выходов дешифратора Yi с активными единичными значениями выходных сигналов (рисунок 9.27, а) можно записать:

![]() ;

;![]() ;

;

![]() ;

;![]() ;

;

![]() ;

;![]() ;

;

![]() ;

;![]() .

.

В таком случае в СДНФ функция мажоритарность в соответствии с таблицей 9.8 может быть представлена в виде

![]() .(9.17)

.(9.17)

Это выражение и реализует схема на рисунке 9.27, а.

Представим ту же функцию в СКНФ и произведем некоторые преобразования по теореме де Моргана:

![]()

![]() .

.

Проанализировав полученное выражение, а также выражения для Yi, приведенные выше, можно окончательно записать:

![]() .(9.18)

.(9.18)

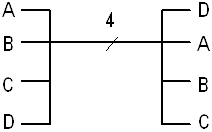

В этом случае трехвходовой мажоритарный элемент может быть реализован на трехвходовом дешифраторе с активными нулевыми значениями выходных сигналов (рисунок 9.27, б).

Рисунок 9.27

Если сравнить между собой реализации КЦУ на основе мультиплексоров и дешифраторов, то можно отметить меньшие аппаратные затраты при использовании мультиплексоров. Однако в конкретных условиях проектирования КЦУ может оказаться целесообразным применение для этих целей и дешифраторов, например, когда половина микросхемы сдвоенного дешифратора уже использована в составе проектируемого устройства, а другая половина осталась свободной и может быть применена для построения какого-либо КЦУ.

9.1.3.3 Построение КЦУ на постоянном запоминающем устройстве (ПЗУ)

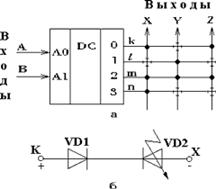

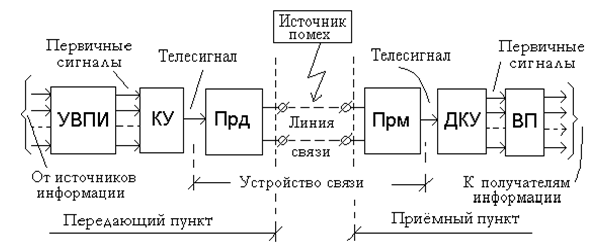

ПЗУ представляет собой большую интегральную схему (БИС), имеющую N входов и М выходов. Упрощенная структура ПЗУ при Nвх=2 и Мвых=3 приведена на рисунке 9.28, а. На входе схемы установлен дешифратор, преобразующий комбинации двухразрядного двоичного кода в четырехпозиционный унитарный (десятичный) код. При каждой комбинации входного ДК на одном из выходов дешифратора появляется логическая 1, а на остальных – нули.

Между выходами дешифратора k, l, m, n и выходными шинами ПЗУ X, Y, Z включены цепочки из двух последовательно включенных диодов VD1 и VD2. На рисунке 9.28, б в качестве примера показана связь между выходной шиной К дешифратора и выходом Х ПЗУ. В исходном состоянии цепочки, связывающие выходы дешифратора и выходы ПЗУ, ток не проводят и связи между шинами k, l, m, n и Х, Y, Z отсутствуют. При этом со всех выходов X, Y, Z снимаются логические нули.

Пользователь на специальном устройстве – программаторе – создает нужные связи между шинами, подавая пробивные напряжения между определенными точками. При этом соответствующие диоды пробиваются, например VD2 (рисунок 9.28, б), и в дальнейшем могут рассматриваться как короткозамкнутые.

На рисунке 9.28, а кружочками показаны созданные постоянные связи, реализующие таблицу истинности комбинационного устройства с тремя выходами (таблица 9.10).

Таблица 9.10

| N | B | A | X | Y | Z | |

| 0 | 0 | 0 | 1 | 0 | 1 | k |

| 1 | 0 | 1 | 0 | 1 | 0 | l |

| 2 | 1 | 0 | 1 | 1 | 1 | m |

| 3 | 1 | 1 | 1 | 0 | 0 | n |

Рисунок 9.28

Например, при комбинации входных логических переменных А=1, В=0 с выходов снимаются сигналы Х=0; Y=1; Z=0. Таким образом на ПЗУ можно реализовать нужную таблицу истинности комбинационного устройства, имеющего несколько выходов. Одна схема ПЗУ может заменить большое число логических микросхем малого и среднего уровня интеграции, поэтому ПЗУ могут эффективно использоваться для создания сложных комбинационных устройств. Кроме того, ПЗУ находят широкое применение как элементы постоянной памяти, в которые заносятся программы, управляющие работой микропроцессоров и однокристальных микроЭВМ.

Похожие работы

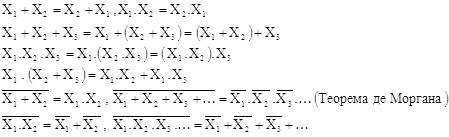

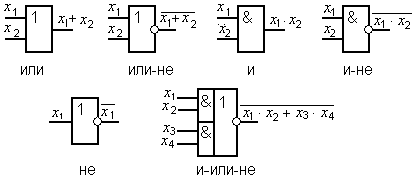

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

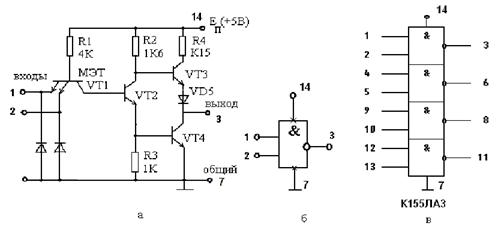

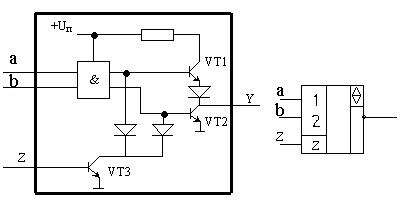

осхемы К155ЛА3 (4 логических элемента 2И-НЕ). Принцип работы ЛЭ И-НЕ ТТЛ Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ ...

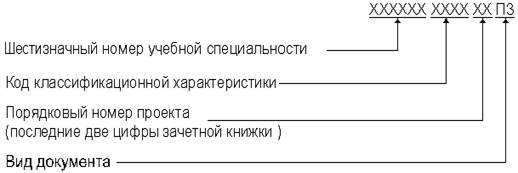

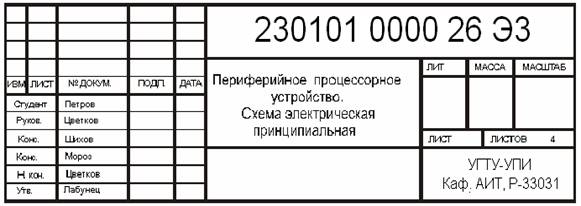

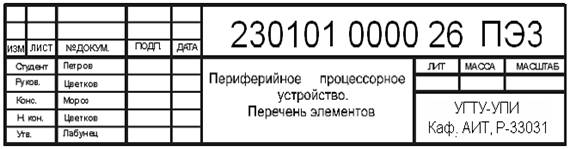

... . Минимальное количество листов графических работ формата А1 — два. Графические документы выполняются карандашом или черной тушью на листах ватмана формата А1. Возможно выполнение чертежей с применением ЭВМ. Допускается использовать формат А2. Листы нумеруются. Номер помещается в верхнем левом углу листа. Допускается выполнять номера на отдельных листах бумаги, которые прикрепляются во время ...

устройств вычислительной техники. Задачи проекта: Разработать печатную плату устройства управления питания компьютерной системы, произвести выбор и обоснование технологического процесса изготовления печатной платы, с исходными данными к проекту: схема электрическая принципиальная. Объём и содержание расчётно-пояснительной записки и графических работ произвести согласно техническому заданию. ...

0 комментариев